|

|

|

Архитектура Астрономия Аудит Биология Ботаника Бухгалтерский учёт Войное дело Генетика География Геология Дизайн Искусство История Кино Кулинария Культура Литература Математика Медицина Металлургия Мифология Музыка Психология Религия Спорт Строительство Техника Транспорт Туризм Усадьба Физика Фотография Химия Экология Электричество Электроника Энергетика |

Комбинационные цифровые устройства

Комбинационное цифровое устройство (КЦУ) – это устройство, выходные сигналы которого в определённый момент времени однозначно определяются входными сигналами. В КЦУ используют не только отдельные логические элементы, реализующие элементарные булевы функции, но и их комбинации, обычно выполненные как единое целое в виде интегральных микросхем. На входы КЦУ подают информационные логические сигналы и сигналы управления, которые определяют порядок передачи информационных входных сигналов на выход и синхронизацию этого процесса. К типовым, широко используемым КЦУ на практике, относятся: преобразователи кодов, шифраторы, дешифраторы, мультиплексоры, демультиплексоры (селекторы), сумматоры цифровые компараторы, а также многовходовые преобразователи типа И-ИЛИ-НЕ. Дешифратор. Дешифратор (decoder, DC) называется КЦУ, преобразующее n–разрядный двоичный код в логический активный сигнал на выходе, десятичный номер которого соответствует входному двоичному коду. Если количество выходов равняется m = 2n, где n – количество входов, то дешифратор называется полный. При меньшем количестве выходов дешифратор будет неполным. На рис 7.20 показано условное обозначение полного дешифратора 3 - 8 и таблица истинности.

Рис.7.20. Данный дешифратор описывается следующей системой логических выражений:

Таким образом, такое КЦУ можно реализовать из восьми одновыходных КЦУ каждое из которых в свою очередь составляют из последовательности базовых элементов. Некоторые типы дешифраторов позволяют преобразовывать двоичную систему счёта в десятичную. На рис.7.21 приведён неполный дешифратор 4-10 с инверсными выходами. Помимо информационных, дешифраторы снабжаются входами разрешения или адресными входами. Это позволяет из более простых дешифраторов строить сложные системы. Например, на рис.7.22 показан дешифратор 4-16 собранный из пяти 2 - 4. Вход активизации дешифратора Е – инверсный.

Рис.7.21.

Рис.7.22. Шифратор. Шифратор (coder, CD) – это комбинационное устройство, преобразующее десятичное число в двоичное. На рис.7.23 показано условное обозначение и реализация шифратора 8 - 3 (восемь входов на три выхода) на базисных элементах.

Рис.7.23. Таблица истинности для данного шифратора имеет вид (Таб.7.1). Функциональные уравнения соответственно равны

По соотношению количества входов m и выходов n шифраторы бывают полные (m = 2n) и неполные (m < 2n). В приоритетных шифраторах выходной двоичный код соответствует наивысшему номеру входа, на который подан активный сигнал (независимо от наличия сигналов на других входах).

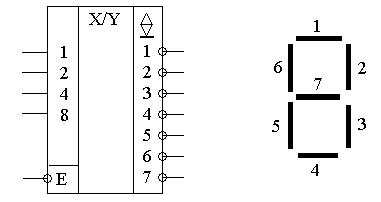

Таб..7.1. Преобразователь кодов. В цифровой технике применяются различные виды кодов для обработки и передачи информации (прямой, обратный, дополнительный, двоично-десятичный, коды Грэя, коды Хемминга и т.д.). Преобразование кодов на аппаратном уровне выполняют комбинационные устройства – преобразователи кодов. К этим устройствам относятся также различные преобразователи управления шкальными, матричными и семисегментными индикаторами. Обозначаются преобразователи кодов через Х/У. Преобразователь кодов часто реализуют по схеме дешифратор – шифратор. Каждый тип преобразователя характеризуется соответствующей таблицей истинности. Частным случаем преобразователей кодов являются шифраторы и дешифраторы. На рис.7.24 показан преобразователь двоично-десятичного кода в код семисегментного индикатора.

Рис.7.24.

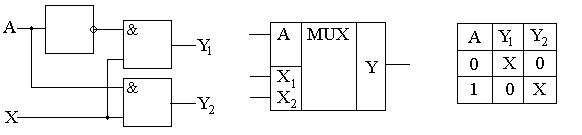

Мультиплексор. Мультиплексор – комбинационное устройство, обеспечивающее передачу цифровой информации, поступающей на несколько входов, на один выход в соответствии с заданным кодом на управляющих входах. По сути это управляемый коммутатор. Также между числом управляющих входов n и числом информационных входов действует соотношение m = 2n для полного мультиплексора, и неполного m < 2n. Мультиплексоры обозначают MUX или MS. На рис.7.25 показана функциональная схема двухвходового мультиплексора, условное обозначение и таблица коммутации.

Рис.7.25. На рис.7.26 показан селектор-мультиплексор 8/1. В зависимости от комбинации сигналов управления Х1Х2Х3 он обеспечивает коммутацию одного из восьми входных сигналов Di на выход У при V – разрешении, активный уровень низкий. Функциональное уравнение записывается в виде

Рис.7.26. Мультиплексоры являются универсальными логическими устройствами, на основе которых создают различные комбинационные и последовательностные схемы. Они используются в делителях частоты, триггерных устройствах, сдвигающих регистрах, преобразователях параллельного кода в последовательный, реализации сложных логических функций. Демультиплексор. Демультиплексор – это цифровое устройство коммутации информационного входного сигнала в один из нескольких выходов в соответствии с заданным кодом на адресных входах. Демультиплексоры обозначают через DMX или DMS. Также по соотношению количества информационных выходов и адресных входов демультиплексоры бывают полными и неполными. На рис.7.27 приведена базовая схема двухвыходного демультиплексора, условное обозначение и таблица функционирования. На рис.7.28 показан демультиплексор четыре в один. Функциональные уравнения, описывающие его работу следующие:

Рис.7.27. Функции демультиплексоров сходны с функциями дешифраторов. Дешифратор можно использовать как демультиплексор. В этом случае информационные входы дешифратора будут служить адресными входами, а входы разрешения дешифратора – информационным входом. КМОП технология позволяет изготавливать двунаправленные ключи, на базе которых созданы объединённые устройства мультиплексоры – демультиплексоры (обозначение MX).

Рис.7.28. Сумматор. Сумматоры – это комбинационные устройства, предназначенные для сложения чисел. Таблица истинности для сложения двух одноразрядных чисел А и В будет

где S – значение суммы, Р – значение переноса в старший разряд. Работа устройства описывается следующими уравнениями

Рис.7.29. Видно, что сумма отвечает логической функции «исключающее ИЛИ» S=AÅB. Устройство, реализующее данную таблицу называют полусумматором и его структура показана на рис.7.29.

Рис.7.30. Одноразрядный полный сумматор строится на основе двух полусумматоров. Его структура и условное обозначение приведены на рис.7.30. В отличие от полусумматора он имеет перенос из младшего разряда. Таблица истинности для сумматора имеет вид

Для суммирования многоразрядных двоичных чисел сумматоры соединяют последовательно, а вывод переноса в младшем разряде соединяют с общим проводом. В виде интегральных схем выпускаются одно, двух и четырёх разрядные сумматоры. С помощью сумматора можно производить и вычитание двоичных чисел. В этом случае операция вычитания заменяется сложением уменьшаемого с вычитаемым в дополнительном коде А – В = А + Вдоп = А + Вобр+1 (7.9).

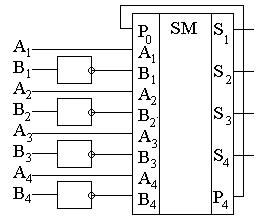

Рис.7.31. На рис.7.31 показан вычитатель на основе четырёхразрядного сумматора. Число В инвертируется и складывается с А, а на перенос подаётся логическая единица.

Поиск по сайту: |

(7.4).

(7.4).

(7.5).

(7.5).

(7.6).

(7.6).

(7.7).

(7.7).

(7.8).

(7.8).