|

|

|

Архитектура Астрономия Аудит Биология Ботаника Бухгалтерский учёт Войное дело Генетика География Геология Дизайн Искусство История Кино Кулинария Культура Литература Математика Медицина Металлургия Мифология Музыка Психология Религия Спорт Строительство Техника Транспорт Туризм Усадьба Физика Фотография Химия Экология Электричество Электроника Энергетика |

Мультиплексоры. Демультиплексоры и дешифраторы

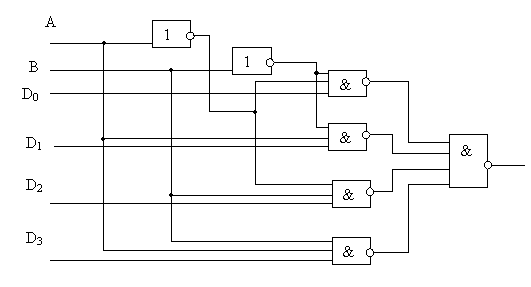

Мультиплексоры –полупроводниковые приборы, которые коммутируют входную информацию, поступающую на разные входные шины на одну выходную в соответствии с информацией на адресном входе. 1. Мультиплексоры 2:1: 2-2и-2или

Если адресных входов (А) – n, то информационных входов (D) – 2n. Может одновременно присутствовать и стробирующий вход управлений всеми информационными входами.

2. Мультиплексор 4:1: увеличение разрядности – пирамидальное наращивание;

Для увеличения разрядности: DD1 – КП7 (8:1) DD2 - ½КП2

D и E – дополнительные коды, которые позволяют выделить какой0то из мультиплексоров, т.е. пропустить его информацию на выход.

КП1 – 16:1 со стробирующим входом. КП2 – это 2 отдельных мультиплексора с общими входами. - Зависимые с общим адресом. Из этого мультиплексора можно получить 2 независимых:

КП5 – без стробирования.

Демультиплексоры и дешифраторы. Демультиплексоры противоположны мультиплексорам. У демультиплексоров сигнал с одного входа распространяется на один из выходов с соответствии с информацией адресного входа. 1:2 1:4 Дешифратор –устройство с несколькими входами и выходами, у которого определенные комбинации входных сигналов соответствует активное состояние одного или нескольких выходов. Увеличение разрядности дешифраторов: UD7

UD3

UD4– сдвоенный дешифратор – демультиплексор с объединенными адресными входами.

Шифраторы являются преобразователями позиционного кода в двоичный. Чтобы устранить неоднозначность при появлении двух «1» на входах, назначается приоритет (более высокий у старшего разряда).

Регистры. Параллельные, последовательные и параллельно-последовательные регистры. Структурные схемы, особенности работы и основные параметры регистров различных типов. Применение регистров в цифровых системах управления. Регистры – функциональные узлы, предназначенные для приема, хранения, передачи и преобразования информации. Используются в качестве управляющих и запоминающих устройств генераторов и преобразователей кодов, счетчиков и делителей частоты, узлов временной задержки. Строятся на синхронных триггерах с динамическим или статическим управлением. Занесение информации в регистр называется операцией ввода или записью. Выдача информации к внешним устройствам характеризует операцию вывода или считывание. Запись информации в регистр не требует его предварительного обнуления. Регистры делятся на: · сдвигающие · накопительные (памяти, хранения) · универсальные. Регистры памятипредназначены для хранения двоичной информации небольшого объема в течение короткого промежутка времени. Представляют собой набор синхронных триггеров, каждый из которых хранит один разряд двоичного числа. Ввод и вывод информации производится одновременно во всех разрядах параллельного кода. Ввод обеспечивается тактовым командным импульсом. Считывание может производиться в прямом и обратном коде (с инверсных выходов). Регистры сдвига. Сущность сдвига – с приходом каждого тактового импульса происходит перезапись (сдвиг) содержимого триггера каждого разряда в соседний разряд без изменения порядка следования «0» и «1». При сдвиге вправо бит из более старшего разряда сдвигается в младший. При сдвиге влево – наоборот. Сдвигающие регистры классифицируются: 1) по способу ввода и вывода информации на: · параллельные · последовательные · комбинированные 2) по направлению сдвига на: · однонаправленные · реверсивные Обозначаются: RG ←, → и ↔ (влево, вправо и реверсивные) Универсальные в зависимости от управляющих сигналов могут выполнять как операцию хранения, так и сдвиг.

4-х разрядный сдвигающий регистр с последовательным вводом. Допустим, что в регистр последовательно вводится начиная с младшего разряда двоичный код 1101, который поступает с внешнего устройства синхронно с тактовыми импульсами. С первым тактовым импульсом в триггер DD1 записывается «1» младшего разряда. Со следующим тактовым импульсом эта «1» будет сдвинута в триггер DD2 и окажется на его выходе. Одновременно в 1-ый триггер запишется «0». После 4-х тактовых импульсов параллельный код на выходах Q1—Q4 будет соответствовать последовательному входному. После пятого тактового импульса сигнал, бывший на выходе Q4 выводится из регистра и пропадает. После 8 тактов регистр полностью очищен. Использование дополнительно логики позволяет вводить информацию параллельно, а считывать последовательно, кроме того регистры сдвигов могут использоваться в составе кольцевых счетчиков (счетчиков Джонсона) применяются для последовательного вывода информации без её стирания.

Для этого информация с выхода регистра по цепи ОС снова вводится на вход. Пока на V единица, информация вводится в регистр по входу D и обратная связь не действует. За n тактов запоминается n разрядный код. Затем на V устанавливается «0» тактовыми импульсами по входу С. Информация с выхода Qn снова вводится в регистр одновременным последовательным (возможно и параллельным) считыванием и через n тактов находится в исходном состоянии. ИР-1

Он может выполнять: · ввод информации параллельным кодом · ввод информации последовательным кодом со сдвигом влево · ввод информации последовательным кодом со сдвигом вправо · хранение. Регистр имеет: · 2 тактовых входа С1 и С2. · управляющий вход выбора режима V2 · 5 информационных входов (V1 для ввода в последовательном коде, D1-D4 для записи в параллельном коде) · 4 выхода Q1-Q4. Ввод информации параллельным кодом осуществляется при V2=1 и C2=0. Сдвиг информации в триггерах происходит по перепаду 1-0 на С2. Входы V1 и C1 при этом блокированы. В этом же режиме по входам V2, С2 производится преобразование последовательного кода в параллельный со сдвигом влево. В этом случае поток информации происходит в обратном направлении. Для этого соединяют Q4 – D3, Q3 – D2, Q2 – D1. Информация подается на D4. Сдвиг влево по перепаду 1-0 на С2.

Во избежание сбоев при смене состояний V2 должна происходить при C1=C2=0. Ввод информации последовательным кодом: входная информация подается на V1, а тактовые импульсы на С1. Сдвиг вправо происходит при каждом перепаде 1à0 тактовых импульсов. ИР-13

ИР-15 4-х разрядный регистр хранения.

EZ – выводы. При EZ1= EZ2=0 – вывод информации, иначе выходы отключены от шин питания и от схемы управления.

ИР-1712-разрядный регистр последовательного приближения

ИР-26 Регистровый файл на четыре 4-х разрядных слова. ИР-27 8-разрядный регистр с разделением записи.

Другие регистры: ИР-11 – 4-х разрядный сдвиговый регистр. ИР-12 – 4-х разрядный параллельный сдвиговый регистр. ИР-16 – универсальный 4-х разрядный сдвиговый регистр. ИР-18 – 6-х разрядный параллельный регистр с D-триггерами. ИР-19 – 4-х разрядный параллельный регистр с O-триггерами. ИР-20 – 4-х разрядный двухкодовый регистр. ИР-21 – 4-х разрядное сдвигающее устройство.

Поиск по сайту: |