|

|

|

Архитектура Астрономия Аудит Биология Ботаника Бухгалтерский учёт Войное дело Генетика География Геология Дизайн Искусство История Кино Кулинария Культура Литература Математика Медицина Металлургия Мифология Музыка Психология Религия Спорт Строительство Техника Транспорт Туризм Усадьба Физика Фотография Химия Экология Электричество Электроника Энергетика |

Арифметико-логические устройства

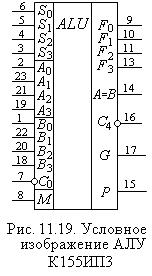

Арифметико-логическим устройством (АЛУ) называется функциональный узел ЭВМ, предназначенный для выполнения арифметических и логических операций по обработке двоичной информации. Основой АЛУ служит сумматор, схема которого дополнена логикой, расширяющей функциональные возможности и обеспечивающей перестройку АЛУ с одной операции на другую, набором регистров и управляющим устройством. Упрощенно схема АЛУ представлена на рис. 11.18. АЛУ имеет входы операндов А и В, входы выбора операций(управляющие сигналы Si и М), вход переноса С. Выходами АЛУ являются результат операции над операндами Fi, сигнал переноса С4, дополнительные выходы образования и распространения ускоренного переноса. Микросхемы АЛУ, принадлежащие к разным видам логик (ТТЛ – 155ИП3; КМОП – 564ИП3), функционально во многом совпадают, в том числе и по разводке выводов. На рис. 11.19 приведено условное изображение микросхемы АЛУ К155ИП3. Эта микросхема выполняет действия с четырехразрядными двоичными На выходах F0, F1, F2, F3 формируются результаты арифметико-логических преобразований. На выходе С4 образуется сигнал старшего (пятого) разряда при выполнении арифметических операций (сигнал переноса). Дополни- Слова А и В, подлежащие обработке, могут быть представлены как в положительной, так и в отрицательной логике. В [9, 15] приведены таблицы функциональной зависимости выходов микросхемы К155ИП3 от состояния входов. Таблицы истинности для каждого варианта логики различны. Старший разряд кода выбора операции (М-вход) определяет характер действий, выполняемых АЛУ. Если М = 1 – АЛУ выполняет логические операции. Если М = 0 – выполняются арифметические и арифметико-логические операции. Рассмотрим более подробно некоторые операции в положительной логике. При М = 1 выполняются логические функции. Если на входах S3S2S1S0 код 0000, то в этом случае выполняется логическая функция инвертирования операнда А – данные со входов А передаются на выходы F с инверсией. Код 0001 – (А V В) с инверсией – поразрядная операция ИЛИ с инверсией над операндами А и В. Код 0010 – операция И инвертированного операнда А и операнда В. Код 0011 – нет операции – логический ноль. Код 0100 – (А Х В) с инверсией – операция И с инверсией. Код 0101 – инверсия операнда В. Код 0110 – операция Исключающее ИЛИ. Код 0111 – операция И над операндами А и инверсией В. При М = 0 выполняются арифметические операции. Результаты арифметических операций выражены в дополнительном коде. Числа в дополнительном и обратном коде связаны соотношением Nдоп = Nобр + 1. Код 0000 – передача на выход операнда А. Код 0001 – А + В – операция суммирования без учета переноса. Код 0010 – (А + Код 0011 – минус 1 (результат арифметической операции представлен в обратном коде). Код 0100 – (А + А Например, последнему рассмотренному коду МS3S2S1S0 = LLHLL (00100) для положительной логики отвечает операция А + А Режим компаратора обеспечивается при М = L и S3S2S1S0 = LHHL (0110). Когда числа А и В равны, на выходе А = В (вывод 14) формируется сигнал высокого уровня. Если числа не равны, то сигнал на выходе С4 характеризует соотношение между числами (в положительной логике табл. 11.7).

Таблица 11.7

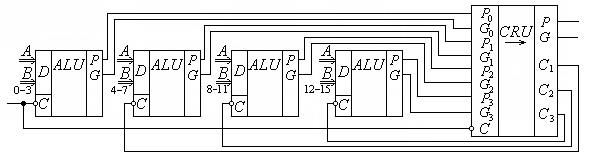

При операциях над словами большой размерности АЛУ соединяются друг с другом с организацией последовательных или параллельных переносов. При последовательном переносе выход С4 предыдущей микросхемы соединяют с входом С0 последующей. При организации параллельного переноса микросхемы 155ИП3 объединяют в сочетании с блоком ускоренного переноса 155ИП4 по схеме, представленной на рис. 11.20.

Рис. 11.20. Увеличение разрядности АЛУ применением блока ускоренного переноса К155ИП4

Выходы С1, С2 и С3 блока ускоренного переноса – сигналы образования и распространения переноса с учетом переносов соответствующих АЛУ. Если при выполнении арифметических операций к быстродействию не предъявляется высоких требований, то при каскадировании АЛУ схемы ускоренного переноса не применяют.

Поиск по сайту: |

По сравнению с приборами, работающими по жесткой, наперед заданной программе, арифметико-логические устройства представляют собой устройства более высокого класса. В микропроцессорной технике АЛУ являются базовыми элементами. Они используются в сочетании с регистрами сдвига, ОЗУ и другими устройствами. АЛУ дороже простых микросхем, но благодаря универсальным свойствам применение их в аппаратуре во многих случаях оказывается оправданным.

По сравнению с приборами, работающими по жесткой, наперед заданной программе, арифметико-логические устройства представляют собой устройства более высокого класса. В микропроцессорной технике АЛУ являются базовыми элементами. Они используются в сочетании с регистрами сдвига, ОЗУ и другими устройствами. АЛУ дороже простых микросхем, но благодаря универсальным свойствам применение их в аппаратуре во многих случаях оказывается оправданным. словами: А = А3А2А1А0 и В = В3В2В1В0. Вид операций задается пятиразрядным кодом установки значений на входах М и S3S2S1S0. Всего это АЛУ способно выполнить 32 операции (25 = 32). К ним относятся: 16 логических операций (И, И-НЕ, ИЛИ, ИЛИ-НЕ, исключающее ИЛИ и др.) и 16 арифметических или арифметико-логических операций (сложение, вычитание, удвоение, сравнение и ряд других). Операции проводятся с ускоренным переносом. Микросхема имеет вход приема сигнала переноса С0 (активный сигнал низкого уровня).

словами: А = А3А2А1А0 и В = В3В2В1В0. Вид операций задается пятиразрядным кодом установки значений на входах М и S3S2S1S0. Всего это АЛУ способно выполнить 32 операции (25 = 32). К ним относятся: 16 логических операций (И, И-НЕ, ИЛИ, ИЛИ-НЕ, исключающее ИЛИ и др.) и 16 арифметических или арифметико-логических операций (сложение, вычитание, удвоение, сравнение и ряд других). Операции проводятся с ускоренным переносом. Микросхема имеет вход приема сигнала переноса С0 (активный сигнал низкого уровня). ) – операция суммирования операнда А с инверсией операнда В без учета переноса.

) – операция суммирования операнда А с инверсией операнда В без учета переноса.