|

|

|

Архитектура Астрономия Аудит Биология Ботаника Бухгалтерский учёт Войное дело Генетика География Геология Дизайн Искусство История Кино Кулинария Культура Литература Математика Медицина Металлургия Мифология Музыка Психология Религия Спорт Строительство Техника Транспорт Туризм Усадьба Физика Фотография Химия Экология Электричество Электроника Энергетика |

ШИФРАТОРЫ И ДЕШИФРАТОРЫ

Шифраторы

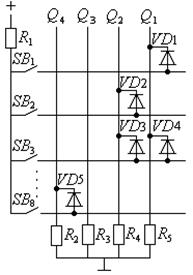

Шифратором называется комбинационное устройство, преобразующее унитарный код, подаваемый на входные шины, в соответствующий код на выходах устройства. Задача шифратора – сформировать код. На вход шифратора могут подаваться различные сигналы: логический 0 или логическая 1 через контакты кнопок клавиатуры управления (кодируется состояние переключателей) или сигналы с других устройств, но во всех случаях происходит преобразование одного сигнала в n-разрядный код (преобразуется унитарный код в позиционный). В таблице истинности шифратора (табл. 10.1) позиционный код представлен двоичным кодом. На рис. 10.1 представлена схема шифратора на диодах.

Таблица 10.1

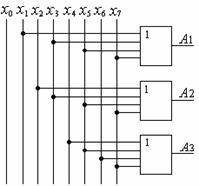

Рис. 10.1. Шифратор на диодах В исходном состоянии, когда ни одна из кнопок не нажата, на всех выводах Q1–Q4 нулевой потенциал. После нажатия на одну из кнопок, например SB3, положительное напряжение, возникшее на делителях R1, R4 и R1, R5, через диоды VD3, VD4 поступает на шины Q1 и Q2. На выходе получается код 0011 – это код нажатой кнопки SB3. Рассмотрим подробнее структуру микросхемы шифратора. Классический шифратор имеет m входов и n выходов, и при подаче сигналов на один из входов (обязательно на один и не более) на выходе узла появляется двоичный код номера возбужденного входа. Число входов и выходов такого шифратора связано соотношением m = 2n. Для построения шифратора можно использовать схемы ИЛИ – по одной на каждый выход. При этом схема разбивается на n простых фрагментов. К входу элементов ИЛИ каждого выходного разряда должны быть подключены те входы шифратора, в двоичном представлении номера которых есть единица в данном разряде. Так, к элементу ИЛИ младшего разряда формируемого выходного кода должны быть подключены все нечетные входы, поскольку у всех нечетных номеров и только у них в младшем разряде содержится единица. Функциональная схема такого шифратора представлена на рис. 10.2. Эту схему можно преобразовать по формулам де Моргана. В новом варианте вместо схем ИЛИбудут схемы И-НЕ.

Рис. 10.2. Функциональная схема шифратора

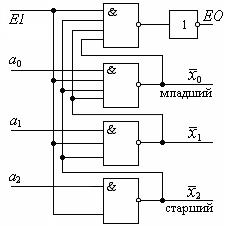

Выше рассмотрен случай использования унитарного кода, при подаче которого на шифратор возбуждается всегда только один его вход. Между тем, в реальных ситуациях возможны случаи, когда одновременно будут возбуждены два и более входа шифратора. Например, в случае ошибочного нажатия одновременно двух и более кнопок (клавиш) произойдёт наложение двух и более унитарных кодов. Для устранения неопределённости, шифратор должен выбрать и преобразовать код только одной кнопки (клавиши). Это достигается использованием схем выбора старшей единицы. В этом случае для преобразования будет выбран код кнопки, в котором 1 стоит на самой старшей позиции. Такая схема вместе с шифратором может входить в состав кодирующего узла. Схема выделения старшей единицы преобразует m-разрядное слово следующим образом: все старшие нули и самая старшая единица входного кода пропускаются на выход без изменения; все разряды более младшие, чем старшая единица, заменяются нулями. На схеме (рис. 10.3) на входы а0, а1, а2 поступает преобразуемое слово (а0 – младший разряд, а2 – старший разряд), на вход EI (от enable in) – входной сигнал разрешения. При EI = 1 схема работает следующим образом: любое число старших нулей порождает на выходах своих разрядов единицы и никак не влияет на работу элементов И-НЕ более младших разрядов. Любая самая старшая единица порождает на соответствующем выходе нуль (активный низкий уровень выхода) и запирает все более младшие элементы И-НЕ, устанавливая на их выходах не активный высокий уровень. При этом низкий уровень появляется и на выходе EO (от enable out) – выходе разрешения.

Рис. 10.3. Схема выделения старшей единицы

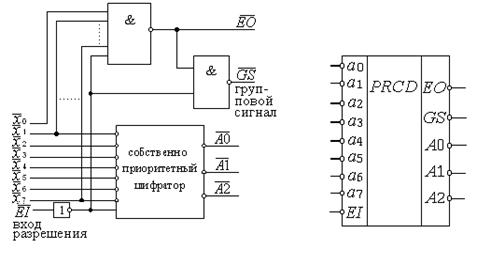

Если разрядность обрабатываемого слова (число входных сигналов) превышает разрядность схемы, то слово разбивается на группы и выход EO более старшей группы подается на вход EI более младшей. При таком включении единица, поступившая на любой вход любой группы, запрет не только все более младшие разряды своей группы, но по цепи EO–EI и все более младшие группы. На выходах всей схемы останется только самая старшая единица входного слова, представленная активным низким уровнем. Если к выходу схемы выделения старшей единицы подключить шифратор, то в сумме получится функциональный узел приоритетного шифратора (priority encoder), формирующий в двоичном коде номер самой старшей единицы из всех, присутствующих во входном слове. С выходами рассмотренной схемы хорошо стыкуются входы шифратора, двойственного по отношению к рассмотренному ранее (т. е. на элементах И-НЕ): инверсным выходам одной схемы (блока выделения старшей единицы) будут соответствовать инверсные входы другой. Весь приоритетный шифратор будет построен на технологичных элементах без лишних инверторов. Если во входном слове присутствует только одна единица, то приоритетный шифратор будет выполнять функцию обычного шифратора. Поэтому микросхемы обычных шифраторов не встречаются почти ни в одной серии, а приоритетные шифраторы – в составе многих серий. Упрощенная структура микросхемы 155ИВ1 и ее обозначение представлены на рис. 10.4. Работу приоритетного шифратора 155ИВ1 отражает таблица истинности (табл. 10.2). Здесь Х – безразличное состояние входа (0 или 1). Из таблицы следует, что вход EI позволяет сделать все входы неактивными (а0-а7) при На выходе GS низкий уровень, если хотя бы на одном входе уровень низкий,

Рис. 10.4. Упрощенная структура приоритетного шифратора и его обозначение

т. е. хотя бы один из входов активный (кроме а0, при этом сигналы А0, А1, А2 и EO высокие). На выходе EO будет низкий уровень, если на всех входах высокие уровни (отсутствуют активные сигналы). Таким образом, выходные сигналы EO и GS характеризуют состояния входов шифратора и используются для каскадирования шифраторов или управления другими логическими схемами:

Каскадирование применяют для увеличения числа входов шифратора, объединяя несколько микросхем шифраторов в один логический узел.

Таблица10.2

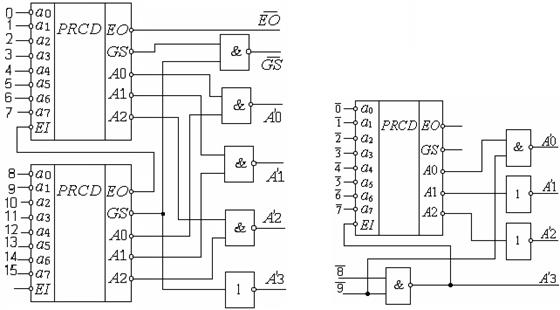

В случае построения шифратора на 16 входов можно объединить два приоритетных шифратора (рис. 10.5). Разряды 8–15 старшего байта входного слова поступают на первый (нижний по схеме) шифратор, а разряды 0–7 младшего байта подаются на второй шифратор (верхний). Информационные выходы обоих шифраторов объединяются с помощью логических элементов. Значение старшего разряда А′3 обеспечивается непосредственно сигналом GS шифратора старшего байта. Для десятичной клавиатуры или декадных переключателей схема может быть реализована с использованием одного восьмивходового шифратора и нескольких дополнительных логических элементов (рис. 10.6).

Рис. 10.5. Шифратор 16:4 Рис. 10.6. Шифратор 10:4

Промышленностью выпускаются микросхемы шифраторов К155ИВ1, 555ИВ1, 555ИВ3 и др.

10.2. Дешифраторы

Дешифратор (декодер) – это комбинационное устройство с несколькими входами и выходами, у которого определенным комбинациям входных сигналов соответствует активное состояние одного из выходов. Дешифраторы преобразуют двоичный или двоично-десятичный код в унитарный код. Если декодер имеет n входов, m выходов и использует все возможные наборы входных переменных, то m = 2n. Такой декодер называют полным. Если используется лишь часть наборов, то такой декодер называют неполным. Дешифраторы используют, когда нужно обращаться к различным цифровым устройствам, и при этом номер устройства (его адрес) представлен двоичным кодом. Входы декодера (адресные входы) часто номеруют не порядковыми номерами, а в соответствии с весами двоичных разрядов, т. е. не 1, 2, 3, 4, а 1, 2, 4, 8. Формально описать работу дешифратора можно, задав список функций, отрабатываемых каждым из его выходов Yi. Так, для дешифратора 3–8:

Yo =

Число входов и выходов декодера указывают следующим образом: декодер 3–8 (читается “три в восемь”); 4–16; 4–10 (это неполный дешифратор). Реализация указанных восьми выражений с помощью восьми трехвходовых элементов И (рис. 10.7) дает наиболее простой по структуре дешифратор, называемый линейным.

а б

Рис. 10.7. Дешифратор 3-8: а – условное обозначение; б – структура

Основной объем его оборудования в общем случае m n-входовых элементов И. Кроме того, к оборудованию обычно относят n инверторов входных переменных и n буферных входных усилителей, сводящих к единице кратность нагрузки источника сигнала. Дешифраторы часто имеют разрешающий вход EI. При EI = 1 дешифратор работает как обычно, а при EI = 0 на всех выходах устанавливаются не активные уровни. Вход EI воздействует на все элементы И. В схеме (рис. 10.8) воздействие оказывается через прямой и инверсный входы одного из разрядов входного кода (через дополнительные элементы И). При этом число входов элементов И не изменяется, но в работу дешифратора вносится дополнительная задержка. В схеме (рис. 10.9) задержка не вносится, но здесь элементы И имеют большее число входов. Разрешающий вход EI часто выполняется инверсным. Дешифратор, имеющий разрешающий вход, иногда называют декодер–демультиплексор и вместо обозначения DC используют обозначение DX. Это связано с тем, что вход EI иногда используют в качестве информационного (как в демультиплексорах).

Рис. 10.8. Разрешение через прямой и Рис. 10.9. Разрешение через инверсный входы одного из разрядов дополнительные входы элементов И

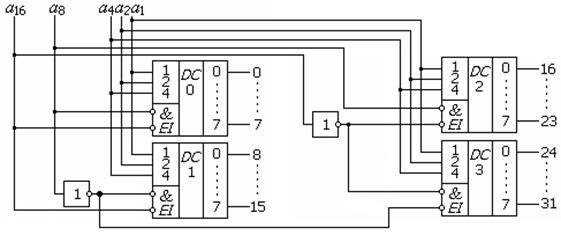

Вход EI используется при построении древовидных (каскадных) схем дешифраторов с целью расширения адресного пространства. При этом все адресное пространство разбивается на группы. Старшие разряды адреса подаются на дешифратор старших разрядов, выходы которого по входам EI управляют дешифраторами второго каскада. На рис. 10.10 представлена схема двухкаскадного дешифратора 5–32 (пять в тридцать два).

Рис. 10.10. Двухкаскадный дешифратор 5–32

Два старших разряда адреса а16 и а8 расшифровываются дешифратором 2–4 DC4, который по входам ЕI управляет четырьмя дешифраторами второго каскада. Младшие разряды адреса а4, а2, а1 поступают на все дешифраторы второго каскада, но открытым по входу EI оказывается лишь один из них. Ему и будет принадлежать единственный из всех 32 возбужденный выход. Например, входной код 01111 у дешифратора DC4 делает активным выход 1. Этим сигналом и откроется дешифратор второй ступени DC1, а DC0, DC2, DC3 закрыты. У дешифратора DC1 сигнал появится на выводе 7, что соответствует 15 выходу всего дешифратора. Такой принцип используется при построении дешифратора на много выходов из микросхем дешифраторов с меньшим числом выходов. В рассмотренном случае 5-разрядный адрес был разбит на две группы в 2 и 3 разряда. Это и определило структуру дешифратора. В общем случае многоразрядный адрес можно разбить на группы различными способами и каждому будет соответствовать свой вариант схемы. Варианты будут различаться задержкой и аппаратными затратами. Таким образом, можно ставить задачу выбора оптимальной, в заданной серии элементов, структуры. На рис. 10.11 показан двухкаскадный дешифратор 4–16, второй каскад которого собран по схеме прямоугольного дешифратора. Разряды адреса разбиты на две группы, каждая из которых независимо от другой расшифровывается своим дешифратором первого каскада DC0 и DC1. При любой комбинации значений входных переменных оказываются выбранными одна строка и один столбец сетки, в узлах которой расположены элементы И второй ступени (второго каскада). В результате каждый входной набор возбуждает выход единственного соответствующего ему элемента И. Такую сетку из элементов И называют прямоугольным или матричным дешифратором.

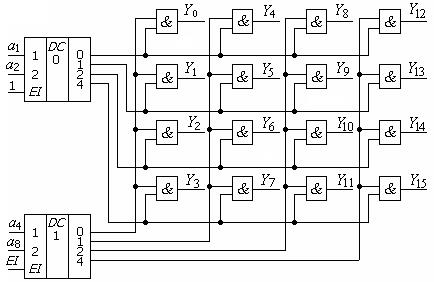

Рис. 10.11. Матричный дешифратор

Делить разряды адреса между DC1 и DC2 нужно по возможности поровну. Чем ближе прямоугольник второго каскада к квадрату, тем, при том же числе выходных элементов И, меньше сумма его строк и столбцов, т. е. меньше число выходов дешифраторов первого каскада. Из этого следует, что использование во втором каскаде квадратной матрицы, позволяет применить в первом каскаде наиболее простые дешифраторы и тем самым минимизировать общую задержку в работе всего дешифратора. В качестве входа EI (Е) всего двухкаскадного дешифратора удобно использовать разрешающий вход только одного из дешифраторов первого каскада. При этом запираются или все строки или все столбцы. Следует отметить, что при большом числе выходов (сотни и более) прямоугольный дешифратор самый экономичный по оборудованию, чем и объясняется его применение в БИС памяти. При малом числе выходов наиболее экономичным является линейный дешифратор. Дешифраторы, выпускаемые в виде микросхем, имеют буквенное обозначение ИД, например, 155ИД3, 155ИД4. В сериях ТТЛ дешифраторы имеют обычно инверсные выходы, т. е. активным является низкий уровень. В КМОП-сериях выходные сигналы чаще имеют активный высокий уровень. Часто в микросхемах дешифраторов делают несколько разрешающих входов, а разрешающей комбинацией является их конъюнкция. При этом удобно наращивать дешифраторы, используя каскадный принцип и строя первый каскад дешифрации не на отдельном специальном дешифраторе, а собирая его из конъюнкторов разрешающих входов. На рис. 10.12 представлен дешифратор 5–32 из 4 дешифраторов 3–8. Каждая микросхема имеет два инверсных разрешающих входа. Символ & над символом ЕI обозначает, что разрешение существует лишь при совпадении всех сигналов группы входов, помеченных знаком &. На рисунке символы инверсии указывают на совпадение двух низких уровней на входах разрешения. Дешифратор первого каскада распределен по конъюнкторам 4 микросхем. Такое решение – иметь несколько разрешающих входов, связанных операцией И, чтобы собирать на этих входах фрагменты дешифраторов, вообще типично для современных микросхем [4, 9, 12, 15].

Рис. 10.12. Дешифрация адресов с использованием в первом каскаде разрешающих входов

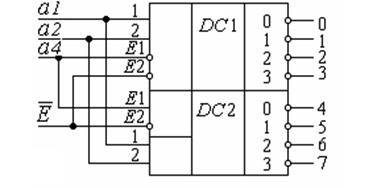

Если использовать только два дешифратора DC0 и DC1, то можно получить дешифратор на 16 выходов. При этом адресный вход а16 будет отсутствовать, а нижние (по схеме) разрешающие входы дешифраторов DC0 и DC1 должны быть заземлены. Схема дешифратора 155ИД4 представлена на рис. 10.13. В нее входят два дешифратора 2–4. Каждый дешифратор имеет пару разрешающих входов. Один разрешающий вход одной из секций инвертирован. Это позволяет, объединив его с неинвертированным разрешающим входом другой секции и подав на эту пару третью переменную а4, использовать ту же самую схему как дешифратор 3–8 с разрешающим входом Е. Кроме того, эта микросхема может быть использована как два демультиплексора с 1 входа на 4 выхода и как демультиплексор с одной линии на 8 выходов.

Рис. 10.13. Схема дешифратора 155ИД4.

Рис. 10.14. Варианты подключения дешифратора 155ИД1

На рис. 10.14 показана возможность использования микросхемы 155ИД1 в качеств дешифратора 4–10 или 3–8. В представленной схеме при использовании всех четырех входов в качестве адресных микросхема представляет дешифратор 4–10. Если вход 8 использовать в качестве разрешающего входа, тогда микросхема будет служить дешифратором 3–8. Выходы 8 и 9 при этом не используются. Дешифраторы могут применяться в качестве демультиплексора входных сигналов, а совместно с шифратором находят применение при построении преобразователей кодов, селектировании заданных входных кодов и др. [11]. Для реализации подобных устройств могут быть использованы программируемые логические матрицы или программируемые логические интегральные схемы (ПЛМ или ПЛИС) [15].

Поиск по сайту: |

= 1, т. е. напряжение высокого уровня на этом входе – это напряжение запрета. При этом и на всех выходах присутствует высокий (неактивный) уровень.

= 1, т. е. напряжение высокого уровня на этом входе – это напряжение запрета. При этом и на всех выходах присутствует высокий (неактивный) уровень.

– выходной сигнал, низкий уровень которого свидетельствует об отсутствии хотя бы одного активного сигнала на входах;

– выходной сигнал, низкий уровень которого свидетельствует об отсутствии хотя бы одного активного сигнала на входах; – выходной сигнал, низкий уровень которого свидетельствует о наличии хотя бы одного активного сигнала на входах.

– выходной сигнал, низкий уровень которого свидетельствует о наличии хотя бы одного активного сигнала на входах.

; Y1=

; Y1=  ; Y2 =

; Y2 =  ; Y3 =

; Y3 =  ; ... Y7 =a4a2a1.

; ... Y7 =a4a2a1.