|

|

|

Архитектура Астрономия Аудит Биология Ботаника Бухгалтерский учёт Войное дело Генетика География Геология Дизайн Искусство История Кино Кулинария Культура Литература Математика Медицина Металлургия Мифология Музыка Психология Религия Спорт Строительство Техника Транспорт Туризм Усадьба Физика Фотография Химия Экология Электричество Электроника Энергетика |

Микросхемы с тремя логическими состояниями

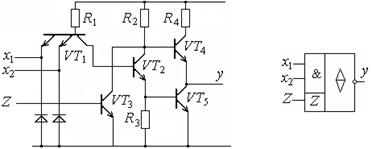

Устройства, оперирующие дискретной информацией, при высоком уровне выходного напряжения имеют малое сопротивление между выводом Выход и шиной питания. В противоположном состоянии у Выхода малое сопротивление по отношению к общей шине. В обоих случаях выходной вывод имеет определенный электрический потенциал, который воздействует на входы последующих приборов. Существует категория микросхем, способных принимать и третье состояние, когда выход микросхемы отключен от нагрузки. В третьем состоянии выходной ток микросхемы пренебрежимо мал. Такое состояние называютвысокоимпедансным. Перевод микросхем в это состояние осуществляется по специальному входу Z. Этот вход часто обозначают ЕZ или ОЕ (Output Enable). В зависимости от конкретного типа микросхемы отключение выхода может осуществляться 1 или 0. Упрощенная электрическая схема элемента с тремя состояниями и ее условное обозначение представлены на рис. 3.31. Когда на входе Z низкий уровень, то VT3 заперт и не влияет на работу схемы. Если вход Z имеет высокий уровень, то транзистор VT3 открыт, коллектор транзистора VT2 имеет нулевой потенциал и, следовательно, ток через него не протекает. При этом эмиттер VT2 также имеет нулевой потенциал. Поскольку базы транзисторов VT4 и VT5 соединены с коллектором и эмиттером VT2, то транзисторы VT4 и VT5 закрыты и выходной провод микросхемы отключен и от плюса источника питания и от общего провода. То есть состояние в отличие от 1 и 0 обозначается буквой Z, и символ такого выхода – ромб с поперечной чертой (рис.3.31.б).

а б

Рис. 3.31. Микросхема с тремя состояниями: а – электрическая схема; б – условное графическое обозначение Другой простой вариант перевода микросхемы в третье состояние представлен на рис. 3.32. В том случае, когда диод VD3 подключен к эмиттеру и коллектору транзисторов VT1 и VT2, а на катод диода подается управляющий сигнал Z с высоким уровнем напряжения (лог. 1), схема работает как элемент 2И–НЕ. Если управляющий сигнал Z представлен низким уровнем напряжения (лог. 0), то эмиттер транзистора VT1 и коллектор транзистора VT2 (а соответственно и база транзистора VT4) подключен через открытый диод VD3 к общему проводу. В этом случае все транзисторы закрыты, и элемент переходит в третье состояние (Z-состояние).

Рис. 3.32. Второй вариант перевода схемы в третье состояние

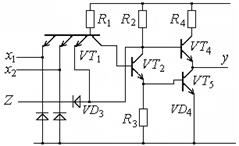

В третьем варианте (рис. 3.33) для перевода схемы в Z-состояние используются транзистор и два диода. Здесь транзистор VT3 соединен непосредственно с базами транзисторов VT4 и VT5 и его состояние определяет потенциал баз этих транзисторов. Диоды VD3 и VD4 между базами транзисторов VT4 и VT5 и коллектором VT3 включены для исключения влияния цепей друг на друга. Если Z = 0, то транзистор закрыт и микросхема работает в обычном режиме. Если Z = 1, то транзистор VT3 открыт, базы транзисторов VT4 и VT5 через диоды и открытый VT3 соединены с общим проводом, т. е имеют нулевой потенциал и транзисторы VT4 и VT5 закрыты.

Рис. 3.33. Вариант схемы с тремя состояниями

В результате связь логической части элемента с его выходом разрывается, элемент со стороны выхода приобретает высокий импеданс. Уровень потенциала на выходе неопределенный (плавающий) – он может быть любым в зависимости от соотношения токов утечки транзисторов VT4 и VT5, если выход схемы ни к чему не подключен. Переход в третье состояние может происходить из 1 в Z, или из 0 в Z. Для элементов с тремя состояниями вводятся следующие временные параметры для задания задержек распространения: t0Z и t1Z – длительность задержки при переходе из низкого или высокого уровней в третье состояние; tZ0 и tZ1 – длительность задержки при переходе из третьего состояния в состояние низкого или высокого уровней соответственно. О микросхемах, выходной сигнал которых может принимать значения 0 или 1, говорят, что это микросхемы типа 2С. Микросхемы с открытым коллектором обозначают ОК (ОС), микросхемы с третьим состоянием – 3С (ТС). Элементы с третьим состоянием выхода разработаны специально для применения в качестве выходного управляемого буфера для подключения цифровых блоков к магистралям, шинам данных. Буфером называют устройство, предназначенное для увеличения мощности, отдаваемой в нагрузку источником сигнала (для увеличения нагрузочной способности источника сигнала). Для этой цели используют микросхемы с выходом ОК. Другая функция буферов – создание двунаправленных линий и мультиплексирование. В этом случае буферы имеют выход 3С. Под двунаправленными линиями понимаются такие линии, сигналы по которым могут распространяться в двух противоположных направлениях. В отличие от однонаправленных линий, которые идут от одного выхода к одному или нескольким входам, к двунаправленной линии могут одновременно подключаться несколько выходов и несколько входов. Двунаправленные линии могут организовываться только на основе выходов 3С, поэтому почти все буферы имеют именно такие выходы. Мультиплексированием называется передача сигналов по одним и тем же линиям в разные моменты времени между разными устройствами. Основная цель мультиплексирования состоит в сокращении общего количества соединительных линий. Двунаправленная линия обязательно является мультиплексированной, а мультиплексированная линия может быть как однонаправленной, так и двунаправленной. Но в любом случае к ней присоединяется несколько выходов, только один из которых в каждый момент времени находится в активном состоянии. Остальные выходы в это время отключаются. С тремя состояниями выхода выпускаются микросхемы различного функционального назначения как комбинационного, так и последовательностного типов. При поочередном действии таких приборов их выходы можно соединять между собой и подключать к общей нагрузке. На рис. 3.34 представлена схема мультиплексирования при работе на общую нагрузку. Выходные сигналы y1, y2,…yn поступают в нагрузку с того элемента, на входе Z которого имеется разрешающий сигнал. Таким способом удается уплотнить каналы передачи данных, а также создавать магистрали с двунаправленными потоками информации. Поскольку выходной каскад буфера построен на основе двух последовательно включенных транзисторов, подача разрешающих сигналов на Z-входы сразу двух буферов магистрали недопустима: результат будет такой же, как и при объединении выходов двух обычных логических элементов.

Рис. 3.34 схема мультиплексирования

В микропроцессорных устройствах в настоящее время широко используют двунаправленные шинные усилители ДНШУ. Следует отметить, что в таких устройствах обычно используются в качестве выходных каскадов не ключевые элементы, выход которых имеет состояние Z. Это позволяет уменьшить уровень импульсных полей – «иголок», возникающих при коммутации мощных быстродействующих ключей. Если в каждый проводник шины данных установить такой усилитель, то, подав на микросхему команду, можно разрешить передачу сигналов по шине данных слева направо или наоборот. На рис. 3.35, а приведена схема одного двунаправленного канала усиления образованного буферными элементами DD1.1 и DD1.2 Эти составные части ДНШУ имеют взаимно инверсные входы разрешения передачи данных: На рис. 3.35, б оба элемента имеют разрешающий вход высокого уровня Z = 1.

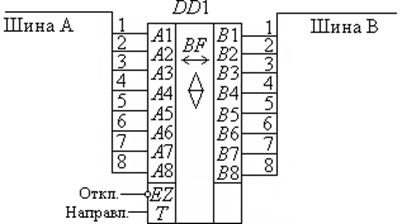

Рис. 3.35. Функциональная схема двунаправленного шинного усилителя: а – передача сигнала по одной линии в обоих направлениях; б – при передаче справа налево – выход на другую линию Для управления направлением передачи сигнала в этой схеме в линию Z одного из элементов следует поставить инвертор. Тогда при Z = 1 сигнал передается справа налево через элемент DD1.2, при Z = 0 – через элемент DD1.2 слева направо. На рис. 3.36 показан пример организации двунаправленной шины с помощью буфера К555АП6. Этот восьмиканальный буфер может передавать данные между двумя двунаправленными шинами А и В в заданном направлении.

Рис. 3.36. Включение двунаправленного буфера

При единичном уровне на управляющем входе Т (сигнал Направл.) данные передаются из шины А в шину В, а при нулевом уровне – из шины В в шину А. Единичный уровень на входе ЕZ отключает микросхему от обеих шин. Микросхемы буферов в отечественной системе обозначений имеют разнообразные обозначения: ЛН, ЛП, АП, ИП, что иногда затрудняет их выбор. Буферы с буквами ЛН имеют инверсию, буферы АП и ИП могут быть с инверсией или без инверсии. Все параметры у буферов довольно близки, отличие в инверсии, в количестве разрядов и в управляющих сигналах Еще два типа выходных каскадов – с открытым эмиттером и с программируемой схемой выхода – будут рассмотрены при изучении микросхем эмиттерно-связанной логики и микросхем на полевых транзисторах.

Поиск по сайту: |

для DD1.1 и Z для DD1.2. Если на вход Z подать напряжение низкого уровня, канал будет передавать данные слева направо через DD1.1 (вход х1, выход у1), поскольку выход нижнего по схеме усилителя DD1.2 разомкнут. При напряжении высокого уровня Z = 1 данные можно передавать по проводнику шины данных справа налево через DD1.2 (вход х2,выход у2). Выход элемента DD1.1 окажется отключенным.

для DD1.1 и Z для DD1.2. Если на вход Z подать напряжение низкого уровня, канал будет передавать данные слева направо через DD1.1 (вход х1, выход у1), поскольку выход нижнего по схеме усилителя DD1.2 разомкнут. При напряжении высокого уровня Z = 1 данные можно передавать по проводнику шины данных справа налево через DD1.2 (вход х2,выход у2). Выход элемента DD1.1 окажется отключенным.