|

|

|

Архитектура Астрономия Аудит Биология Ботаника Бухгалтерский учёт Войное дело Генетика География Геология Дизайн Искусство История Кино Кулинария Культура Литература Математика Медицина Металлургия Мифология Музыка Психология Религия Спорт Строительство Техника Транспорт Туризм Усадьба Физика Фотография Химия Экология Электричество Электроника Энергетика |

Двухступенчатые триггеры

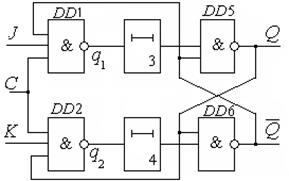

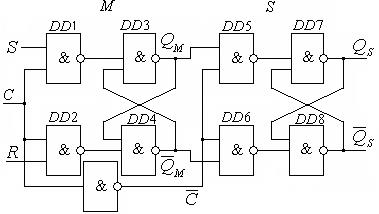

На рис. 6.12 показана схема, состоящая из двух последовательно включенных синхронных RS-триггеров, первый из которых называется ведущим или М-триггером (от master – хозяин), а второй – ведомым или S-триггером (от slave – подчиненный). Благодаря общему синхросигналу С вся схема функционирует как единое целое и называется двухступенчатым или MS-триггером (master-slave flip-flop).

Рис. 6.12. Схема MS-триггера

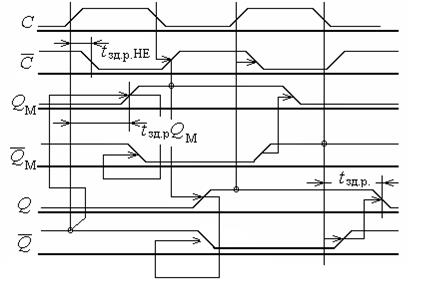

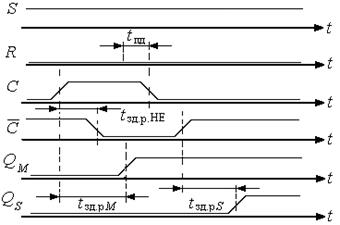

Из временной диаграммы (рис. 6.13) видно, что информация, задаваемая уровнями на входах S и R, по фронту С-сигнала принимается в М-триггер, но в течение всего времени, пока С-сигнал равен 1, не проходит в S-триггер, поскольку его входные конъюнкторы DD5 и DD6 в это время перекрыты инверсией С-сигнала – сигналом Отсюда важное отличие MS-триггера от триггера-защелки: MS-триггер непрозрачен по управляющим R- и S-входам ни при С = 0, ни при С = 1. Каждая ступень его сама по себе прозрачна, но включены ступени последовательно, и какая-нибудь из них всегда остается запертой – или синхросигналом, или его отсутствием. Таким образом, в MS-триггере никакое изменение на управляющем входе не может само по себе, без переключения сигнала С проникнуть на выход. Триггер может изменить состояние выхода только по срезу С-сигнала. Между тем, как и для синхронного RS триггера, построенного на элементах И-НЕ(см. таблицу 6.5), комбинация сигналов S=R=1 объявляется запрещенной, поскольку приводит триггер в неопределенное состояние.

Рис. 6.13. Временная диаграмма работы MS-триггера

Следует отметить также, что появлению среза сигнала С должен предшествовать интервал времени подготовки tпд, в течение которого сигналы на S- и R- входах не должны изменяться. Если такого интервала не было, т.е. перед появлением среза С было изменение S- или R-сигнала и переключение М-триггера, эти процессы могут наложиться и работа MS-триггера будет неустойчивой.

6.7. JK-триггеры

Этот тип триггеров не имеет неопределенных состояний. Функциональная особенность JK-триггера состоит в том, что при всех входных комбинациях, кроме одной Jn = Kn = 1, они действуют подобно RS-триггеру, причем вход J играет роль входа S, а К-вход соответствует R-входу, С – тактовый вход. При входной комбинации Jn = Kn = 1 в каждом такте происходит опрокидывание триггера и выходные сигналы меняют свое значение. JK-триггеры относятся к универсальным устройствам. Они с равным успехом могут использоваться в регистрах, счетчиках, делителях частоты и других узлах. Путем определенного соединения выходов JK-триггеры легко обращаются в триггеры других типов. Это позволяет промышленности сократить номенклатуру триггеров, не сковывая в то же время разработчиков аппаратуры. Состояния JK-триггера при различных комбинациях входных сигналов представлены в табл. 6.8. Таблица 6.8

По способу управления JK-триггеры, также как и RS-триггеры, могут быть синхронными и асинхронными. Применяют, однако, только синхронные, так как асинхронные предъявляют жесткие требования к длительности входных импульсов. В схемном отношении JK-триггеры отличаются от RS-триггеров наличием обратной связи с выходов на входы. Схема простейшего JK-триггера представлена на рис. 6.14. Из схемы следует, что состояние JK-триггера зависит не только от J и K, но и от Q и

Рис. 6.14. Структура JK-триггера с элементами временной задержки

При Jn = Kn = 0 на выходах элементов DD1 и DD2 будет q1 = q2= 1 (независимо от значений Q и Когда Jn ¹ Kn, выходное состояние триггера будет определяться элементом DD 1 или DD 2, на входах которого действует логическая 1. Входная комбинация Jn = Kn = 1 при любом состоянии триггера вызывает его переброс. Действительно, если Qn = 1 и Qинвn = 0, то q1 = 1, а q2 = 0 (т.к. Кn = Qn = 1). Сигнал q2 переключит триггер в состояние Qинвn+1 = 1 и Qn+1 = 0. Переброс будет и при Qn = 0, а Назначение цепей временной задержки 3 и 4 – создание временного сдвига между моментом ввода входной информации и началом формирования выходной (Qn и Предупреждение генерации просто и эффективно обеспечивается в триггерах с двухступенчатым управлением. Схема двухступенчатого JK-триггера с инвертором в цепи синхронизации представлена на рис. 6.15. Двухступенчатый JK-триггер – непрозрачный триггер, выходы его петлями инвертирующих обратных связей (накрест) заведены на входные конъюнкторы DD1 и DD2. При J = K = 0 С-сигнал не может открыть входные элементы DD1 и DD2 и триггер находится в режиме хранения. При J = 1, K = 0 синхросигналом может быть открыт лишь элемент DD 1 и только при условии, что перед поступлением С-сигнала на выходе триггера был 0: Q = 0,

Рис. 6.15. Двухступенчатый JK-триггер с инвертором в цепи синхронизации

Если же триггер до синхросигнала был в 1, то он так и останется в 1. Таким образом, J-вход выполняет функции синхронизированного S-входа. В силу симметрии схемы легко показать, что К-вход выполняет функции синхронизированного R-входа, переводя триггер в 0. Поэтому при разноименных уровнях на J- и К-входах JK-триггер ведет себя как синхронный непрозрачный RS-триггер. Существенно отлично от RS-триггера поведение JK-триггера при J = K = 1. Для RS-триггера такое состояние запрещено. Диаграмма работы JK-триггера в этом режиме приведена на рис. 6.16. При любом состоянии триггера сигналы обратной связи открывают для С-сигнала именно тот конъюнктор, пройдя через который С-сигнал переведет триггер в противоположное состояние. Таким образом, при J = K = 1 по срезу каждого С-сигнала JK-триггер меняет свое состояние на противоположное. Это уже известный четный режим. Режимы работы JK-триггера представлены в табл. 6.9.

Рис. 6.16. Временная диаграмма работы JK-триггера в счетном режиме

Таблица 6.9

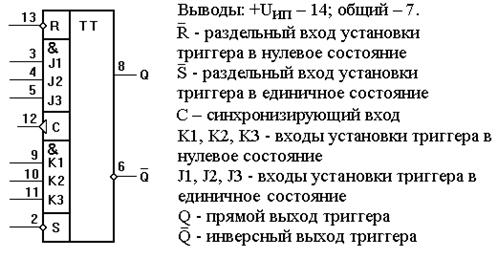

Следует отметить, что серийно выпускаемые JK-триггеры имеют по нескольку конъюнктивно связанных J- и К-входов. Примером тому является микросхема К155ТВ1. Это JK-триггер, имеющий тройные конъюнктивные входы J и К, а также асинхронные входы Rа и Sа для установки триггера в состояние 0 ипи 1 независимо от сигналов на информационных и тактирующем входе. Условное обозначение этого триггера приведено на рис.6.18.

Рис. 6.17 Условное обозначение JK-триггера K155TB1

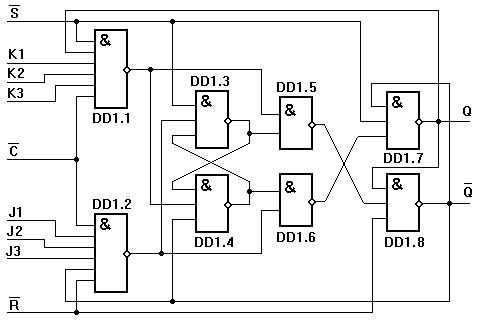

Внутренняя структура этого триггера близка к структуре JK-триггера, рассмотренной ранее (рис. 6.16), и приведена на рис 6.18. Известны и другие разновидности JK триггеров: JK-триггер с запоминающими связями, JK-триггер, переключаемый фронтом, шестиэлементный триггер, JK-триггер, использующий задержку. Более подробные сведения о JK-триггере можно получить в справочной литературе, например [9].

Рис. 6.18 Внутренняя структура JK-триггера K155TB1

СЧЕТЧИКИ

Общие положения

Счетчиком называют устройство, сигналы, на выходе которого, в определенном коде отображают число импульсов, поступивших на счетный вход. Триггер Т-типа может служить примером простейшего счетчика. Такой счетчик считает до двух. Счетчик, образованный цепочкой из m триггеров, соединенных определенным образом, может посчитать в двоичном коде 2m импульсов. Каждый из триггеров цепочки называют разрядом счетчика. Число m определяет количество разрядов двоичного числа, которое может быть записано в счетчик. Число Ксч = 2m называют коэффициентом (модулем) счета. Информация снимается с прямых и (или) инверсных выходов всех триггеров. В паузах между входными импульсами триггеры сохраняют свое состояние, т. е. счетчик запоминает число сосчитанных импульсов. Нулевое состояние всех триггеров принимается за нулевое состояние счетчика в целом. После каждого цикла счета на выходах последнего триггера возникают перепады напряжения. Это свойство определяет второе назначение счетчиков: деление числа входных импульсов. Если входные сигналы периодичны и следуют с частотой fвх, то частота выходных импульсов будет fвых = fвх/Ксч. У счетчиков в режиме деления частоты используется только выходной сигнал последнего триггера. Такие делители имеют целочисленный коэффициент деления. Элементная база современной микроэлектроники позволяет строить делители и с дробным коэффициентом деления. На схемах счетчик обозначают буквами СТ (от counter – счетчик), иногда проставляют модуль счёта, например: СТ2 - двойной счетчик; СТ2/10 – двоично-десятичный счетчик. В обозначении счетчиков имеются буквы ИЕ, например, К155ИЕ2, К155ИЕ6. Основные эксплуатационные показатели: емкость и быстродействие. Емкость равна коэффициенту счета – число импульсов, доступное счету за один цикл. Быстродействие определяется разрешающей способностью tразр.сч. Это минимальное время (min t) между двумя входными сигналами, при котором еще не возникают сбои в работе счетчика. Обратная величина fmax = 1/tразр.сч. называется максимальной частотой счета. Время установки кода tуст равно времени между моментом поступления входного сигнала и переходом счетчика в новое состояние. При этом tуст всегда < tразр. сч. Временные свойства зависят от временных характеристик триггеров и способа их соединения между собой.

Поиск по сайту: |

. Они откроются лишь при

. Они откроются лишь при  , т.е. на срезе С-сигнала, и только тогда S-триггер примет состояние М-триггера.

, т.е. на срезе С-сигнала, и только тогда S-триггер примет состояние М-триггера.

n

n