|

|

|

Архитектура Астрономия Аудит Биология Ботаника Бухгалтерский учёт Войное дело Генетика География Геология Дизайн Искусство История Кино Кулинария Культура Литература Математика Медицина Металлургия Мифология Музыка Психология Религия Спорт Строительство Техника Транспорт Туризм Усадьба Физика Фотография Химия Экология Электричество Электроника Энергетика |

Що таке тригери? Де вони використовуються? Наведіть приклади

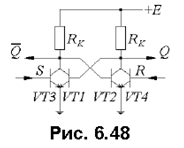

Тригер являє собою двокаскадний підсилювач постійної напруги (ППН), у якого вихід приєднаний безпосередньо до входу. Тригер має здатність фіксувати та ”запам’ятовувати” факт надходження на один з його входів запускаючого імпульсу. Короткочасний, тривалістю лише у частки мікросекунди, пусковий імпульс здатний призвести до того, що режим тригера зміниться і в такому “перекинутому” стані тригер буде перебувати як завгодно довгий час, аж поки новий пусковий імпульс, поданий на протилежний вхід не поверне тригер до його попереднього стану. Ця властивість тригера, що має назву ”електронної пам’яті”, широко використовується в електроніці для фіксування та зберігання цифрової інформації, яка, як відомо, передається у вигляді коротких прямокутних імпульсів. Тригер, що є елементарною коміркою в складних системах електронної пам’яті мікропроцесорів та ЕОМ, фіксує факт надходження такого окремого імпульсу, зберігає інформацію про це та може видавати її при відповідному запиті. Схема асинхронного RS-тригера наведена на рис. 6.48, а його таблиця істинності – в табл. 6.18.

Транзистори VT1 та VT2 разом з опорами RK складають основу тригера. Транзистори VT3 та VT4 – використовуються для його запуску. Коли на входах тригера S=“1” та R=“0”, транзистор VT3 відкривається і на колекторах VT1 і VT3 та на базі VT2 встановлюється “0”. Транзистор VT2 – закривається і на виході Q встановлюється “1”, а на так званому інверсному виході Q – “0”. При зворотній комбінації вхідних сигналів на виході Q встановлюється “0”, а на виході Q – “1”. При комбінації S=“0” та R=“0” можливий стан, коли Q =“1”, але можливий стан, коли Q=“0”. Отже, при цій комбінації вхідних сигналів тригер зберігає той стан, у який він був попередньо встановлений. Це режим зберігання записаної в тригер інформації. При комбінації вхідних сигналів S=“1” та R=“1” на колекторах VT1 та VT2 буде “0”. При одночасній зміні вхідних сигналів неможливо передбачити, у який стан встановиться тригер, тому ця комбінація вхідних сигналів є забороненою і її слід уникати. Зображений на рис. 6.48 тригер є не що інше, як пара з’єднаних між собою логічних елементів “АБО-НЕ”, як це показано на рис. 6.49, а. Але асинхронний RS-тригер легко створити також з логічних елементів “І-НЕ”, як це показано на рис. 6.49, б.

Тригер, створений з елементів “І-НЕ” (його ще називають RS-тригер з інверсними входами) має таблицю істинності, наведену в табл. 6.19. Тут за режим зберігання відповідає комбінація вхідних сигналів S=“1” та R=“1”, а комбінація S=“0” та R=“0” – є забороненою. Умовне позначення асинхронного RS-тригера наведено на рис. 6.5.0

Синхронний RS-тригер відрізняється від асинхронного тим, що крім інформаційних S- та R-входів він має ще “дозволяючий” С-вхід (рис. 6.51).

“Провідний” тригер Т1 спрацьовує від вхідних інформаційних сигналів за наявності логічної одиниці на його синхронізуючому вході. “Підлеглий” тригер Т2 повинен сприйняти інформацію від “провідного” і відтворити її на своїх виходах лише по закінченні сигналу С=“1”. Для цього синхронізуючий сигнал подається на С-вхід “підлеглого” тригера через інвертор, який блокує його роботу до моменту закінчення імпульсу синхронізації. Умовне позначення затриманого синхронного тригера наведено на рис. 6.54.

Дві літери “Т” означають, що тригер двоступеневий, тобто складається із “провідного” та “підлеглого”. У такому затриманому синхронному RS-тригері акти встановлення та перевстановлення відбуваються в моменти закінчення вхідного С- сигналу, тобто в моменти його перепаду від високого рівня до низького. Таке перемикання прийнять називати “за зрізом” сигналу синхронізації. На схемах синхровхід, що здійснює перемикання за зрізом, позначають трикутником вістрям назовні, або спадною косою рискою (рис. 6.54, а, б). Якщо ж перемикання відбувається в моменти початку вхідного С-сигналу, тобто в моменти його перепаду від низького рівня до високого, то воно називається “за фронтом” сигналу синхронізації; такий С-вхід позначають трикутником вістрям усередину, або зростаючою косою рискою (рис. 6.54, в, г). Подібні тригери, які спрацьовують по фронтах синхронізуючого сигналу, називаються динамічними. D-тригер, або “тригер пам’яті”, є найпростішим за принципом дії. Він має лише один інформаційний D-вхід та синхронізуючий вхід С (рис. 6.55).

Коли С=“1” то на Q-виході цього тригера встановлюється стан, що відповідає вхідному. При С=“0” попередньо встановлений стан зберігається (таблиця істинності D-тригера наведена в табл. 6.20). Іноді D-тригер наділяють установчим R- входом, для безумовного встановлення тригера у стан Q =“0” незалежно від сигналів на С- та D-входах. Аналогічно може діяти і установчий S-вхід, який безумовно встановлює Q =“1”.

Часто виникає потреба у тригері, який змінює свій стан при кожному такті синхроімпульсу. У якості керуючого фронту використовують передній або задній фронт тактового С-сигналу. Такий тригер називають Т-тригером; він має лише один вхід – Т. Він перемикається щоразу, коли на Т-вході сигнал змінюється від рівня логічної одиниці до логічного нуля (рис. 6.56, а), або від рівня логічного нуля до логічної одиниці (рис. 6.56, б). Оскільки перемикання тригера викликане кожним імпульсом, що надходить на його Т-вхід, то такий режим роботи тригера називають лічильним, а сам тригер – лічильним тригером. Лічильний тригер легко побудувати на базі синхронного затриманого RS-тригера, якщо подати негативний зворотній зв’язок з його виходів на входи, як це показано на рис. 6.56, в.

Найбільш універсальним є JK-тригер (рис. 6.57, а), який, як і Т-тригер, можна побудувати на базі затриманого синхронного RS-тригера. Для цього необхідно подати негативний зворотній зв’язок з виходів на R- та S-входи, подібно до Т-тригера, проте у логічних елементах “І-НЕ”, що створюють вхідні кола “провідного” синхронного RS-тригера додати ще по одному інформаційному входу. Це і будуть J- та K- входи. Універсальність JK-тригера полягає в тому, що відповідним з’єднанням J- та K-входів його можна перетворити на будь-який інший з розглянутих нами тригерів. Наприклад, якщо додаванням інвертора забезпечити умову K = J , то по зрізу C-сигналу тригер буде встановлювати на Q-виході сигнал, який відповідатиме вхідному J-сигналу і буде зберігати цей стан навіть після зняття С-сигналу. Тобто JK-тригер працюватиме як затриманий D-тригер. Якщо ж з’єднати J- та K-входи та подати на них логічну одиницю (J=K=“1”), то кожний черговий імпульс на С-вході викликатиме перемикання тригера. Така схема є подібною до Т-тригера. Окрім перелічених вище J-, C- та K-входів JK-тригер іноді обладнують установчими R- та S-входами, як це показано на рис. 6.57, б.

Поиск по сайту: |

Цей тригер реагує на сигнали на інформаційних входах лише за умови С=“1”. Умовне позначення синхронного RS-тригера наведено на рис. 6.52. Іноді виникає потреба одержати на виході синхронного тригера відгук на вхідний сигнал не в момент коли (і поки) діє синхронізуючий С сигнал, а лише по його закінченні. Для реалізації такої дії створюють затриманий синхронний RS-тригер. Він складається з двох синхронних RS-тригерів: “провідного” Т1 та “підлеглого”, Т2 як це показано на рис. 6.53.

Цей тригер реагує на сигнали на інформаційних входах лише за умови С=“1”. Умовне позначення синхронного RS-тригера наведено на рис. 6.52. Іноді виникає потреба одержати на виході синхронного тригера відгук на вхідний сигнал не в момент коли (і поки) діє синхронізуючий С сигнал, а лише по його закінченні. Для реалізації такої дії створюють затриманий синхронний RS-тригер. Він складається з двох синхронних RS-тригерів: “провідного” Т1 та “підлеглого”, Т2 як це показано на рис. 6.53.