|

|

|

Архитектура Астрономия Аудит Биология Ботаника Бухгалтерский учёт Войное дело Генетика География Геология Дизайн Искусство История Кино Кулинария Культура Литература Математика Медицина Металлургия Мифология Музыка Психология Религия Спорт Строительство Техника Транспорт Туризм Усадьба Физика Фотография Химия Экология Электричество Электроника Энергетика |

Работа в режиме счетчика

В режиме счетчика таймеры/счетчики могут осуществлять счет сигналов от внешних источников, импульсов тактовой частоты микроконтроллера (СК) или импульсы с выходов делителей частоты. Таймеры/счетчики ТС0 и ТС1 используют выходы ступеней деления общего 10-разрядного предварительного делителя (рис. 13.2). Выбор источников тактовых сигналов обеспечивается комбинацией значений битов, установленных в регистрах управления TCCR0 и TCCR1В соответственно. Предварительный делитель таймеров/счетчиков 0 и 1 содержит четыре ступени деления: СК/8, СК/64, СК/256 и СК/1024, где СК – входной тактовый сигнал. Кроме того, в качестве источников тактовых сигналов могут быть использованы сигналы от внешних источников, тактовый сигнал СК и нулевой тактовый сигнал (stop), также могут быть использованы как часы.

Рис. 13.2. Предварительные делители таймеров/счетчиков 0 и 1

Таймер/счетчик ТС2 имеет собственный 10-разрядный предварительный делитель (рис. 13.3).

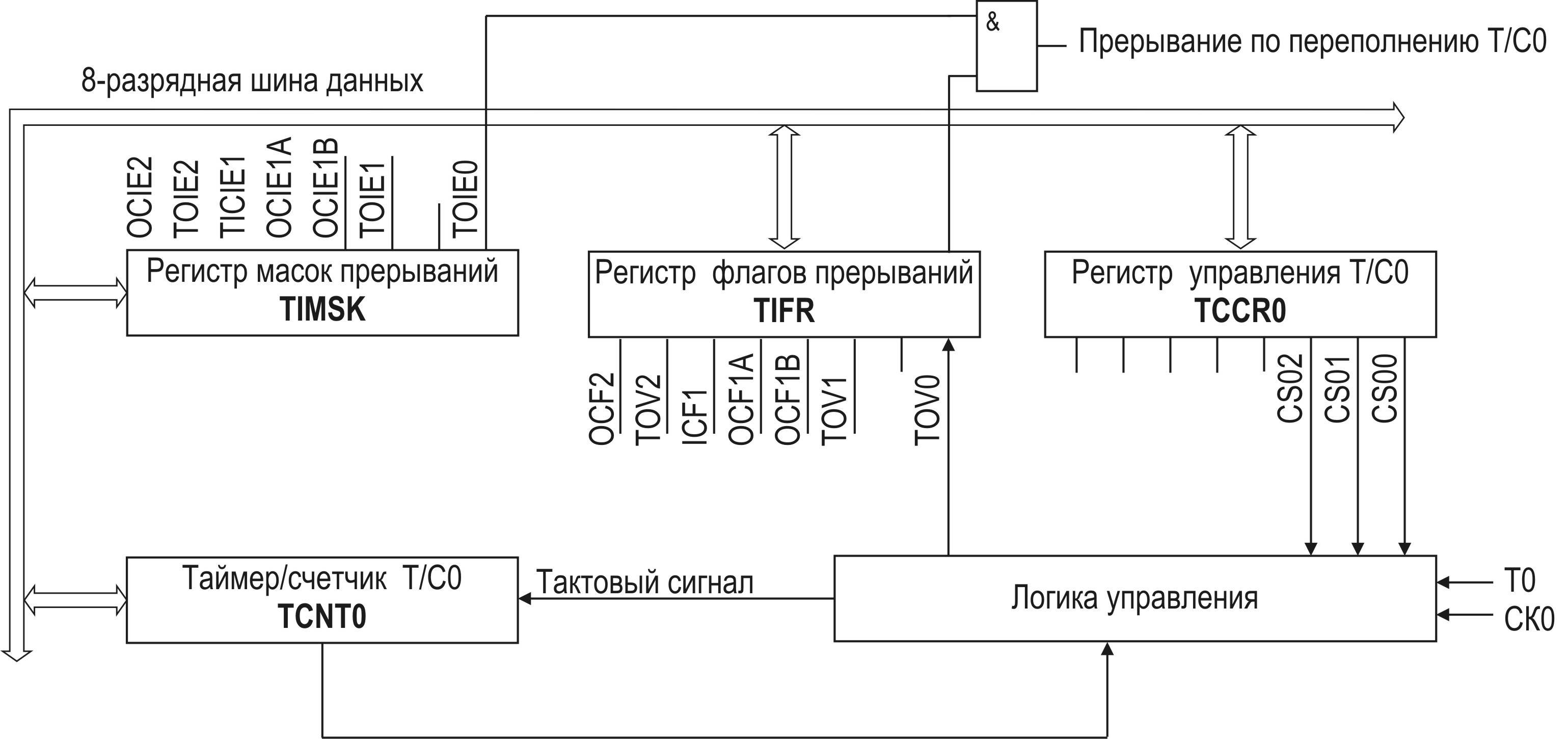

Рис. 13.3. Предварительный делитель таймера/счетчика 2 Тактовый сигнал таймера/счетчика 2 обозначен РСК2. Этот тактовый сигнал по умолчанию подключен к основному тактовому сигналу системы СК. При установке бита AS2 в регистре ASSR таймер/счетчик 2 будет асинхронно тактироваться сигналом с вывода PC6 (TOSC1), что позволяет использовать таймер/счетчик 2 в качестве часов реального времени (RTC), когда AS2 установлен таким образом, что соединяет PC6 (TOSC1) и PC7 (TOSC2) через разъединительный порт С. Генератор оптимизирован под использование кварцевого кристалла с частотой 32,768 кГц, подсоединяемого между выводами PC6 (TOSC1) и PC7 (TOSC2). При тактировании таймера/счетчика 2 внешним тактовым сигналом, этот сигнал синхронизируется с тактовой частотой CPU. Для обеспечения правильной синхронизации внешнего сигнала необходимо, чтобы минимальное время между двумя входящими тактовыми циклами было не менее одного цикла внутреннего тактового сигнала CPU. Внешний тактовый сигнал синхронизируется нарастающим фронтом внутреннего тактового сигнала CPU. Частота внешнего тактового сигнала, подаваемого на вывод TOSC1, не должна превышать одной четвертой от тактовой частоты процессора, но не выше чем 256 кГц. На рис. 13.4 показана блок-схема таймера/счетчика 0.

Рис. 13.4. Блок-схема таймера/счетчика 0

8-разрядный таймер-счетчик 0 получает тактовый сигнал или непосредственно от СК или от внешнего вывода. Кроме этого, таймер-счетчик 0 может быть остановлен, как это показано в описании регистра управления Timer/Counter0 – TCCR0. В регистре флагов прерывания таймера-счетчика 0 TIFR хранится флаг состояния переполнения. Установки управляющих сигналов хранятся в регистре управления таймером/счетчиком – TCCR0. Установка разрешения/запрещения прерываний производится в регистре масок прерываний таймеров/счетчиков – TIMSK. Точность и разрешение 8-разрядных таймеров/счетчиков растет с уменьшением коэффициента предварительного деления. Аналогичным образом высокий коэффициент предварительного деления удобно использовать при реализации функций с низким быстродействием или при точной синхронизации редко происходящих действий.

Регистр управления таймером/счетчиком 0 – TCCR0 (The Timer/Counter0 Control Register)

Биты 2, 1 и 0 выбора тактовой частоты TС0 подключают выход определенной ступени предварительного делителя. Величину коэффициента деления частоты определяют комбинации значений битов, приведенные в таблице 13.6. Если таймер/счетчик 0 используется как счетчик, то вывод Т0 конфигурируется как вход. Таймер/счетчик 0 осуществляет счет в регистре TCNT0 Регистр счета таймера/счетчика 0 – TCNT0

Timer/Counter 0 реализован как счетчик с возможностью чтения/записи. Если в Timer/Counter 0 записано некоторое значение и выбран источник тактового сигнала, то он продолжит счет с записанного значения с тактовой частотой счетчика. Таблица 13.6. Выбор коэффициента деления предварительного делителя частоты таймера/счетчика 0

Установки управляющих сигналов таймера/счетчика 1 хранятся в регистре управления таймером/счетчиком – TCCR1B. Биты 2, 1 и 0 выбора тактовой частоты TС1 подключают выход определенной ступени предварительного делителя. Величину коэффициента деления частоты определяют комбинации значений битов, приведенные в таблице 13.7. Регистр управления B таймера/счетчика 1 – TCCR1B

Таблица 13.7. – Выбор источника тактового сигнала таймера/счетчика1

Если таймер/счетчик 1 используется как счетчик, то вывод Т1 конфигурируется как вход. Таймер/счетчик 1 осуществляет счет в регистрах TCNT1H и TCNT1L. Установки управляющих сигналов таймера/счетчика 2 хранятся в регистре управления таймером/счетчиком – TCCR2. Величину коэффициента деления частоты определяют комбинации значений битов2, 1 и 0, приведенные в таблице 13.8. Регистр управления таймером/счетчиком 2 – TCCR2

Таблица 13.8. Выбор источника тактового сигнала таймера/счетчика2

Поиск по сайту: |