|

|

|

Архитектура Астрономия Аудит Биология Ботаника Бухгалтерский учёт Войное дело Генетика География Геология Дизайн Искусство История Кино Кулинария Культура Литература Математика Медицина Металлургия Мифология Музыка Психология Религия Спорт Строительство Техника Транспорт Туризм Усадьба Физика Фотография Химия Экология Электричество Электроника Энергетика |

Цифровые запоминающие устройства ⇐ ПредыдущаяСтр 3 из 3

Цифровыми запоминающими устройствами называют устройства, предназначенные для записи, хранения и считывания информации, представленной в цифровом коде. Запоминающие устройства (ЗУ) классифицируют по назначению, технологии изготовления. Способу адресации. Способу хранения информации и т.д. По назначению ОЗУ и ПЗУ. ПЗУ классифицируют на программируемые при изготовлении (ПЗУ, ROM) С однократным программированием (ППЗУ, РROM) Перепрограммируемые с ультрофиолетовым или электрическим стиранием информации. Флеш-память имеет ряд особенностей. В ней осуществляется стирание или всей записанной информации одновременно, или больших блоков информации , а не тирание отдельных слов, предназначена для хранения редко обновляемой информации и замены памяти на магнитных дисках в портативных компьютерах. Программируемые логические интегральные схемы Изготовление заказных больших и сверхбольших интегральных схем (БИС, СБИС) это длительный и дорогостоящий процесс. Решение проблемы найдено через создание универсальных логических устройств большой степени интеграции, алгоритмы которых задаются разработчиком (ПЛИС). Программируемые управляющие устройства нашли широкое применение в системах управления различными технологическими процессами, совокупность арифметико-логического устройства, регистров общего назначения, устройств запоминающих, устройств ввода-вывода и др. реализуется в виде отдельных или общих микросхемах. Мозгом микропроцессоров является арифметико-логическое устройство, которое представляет собой логический комбинационный автомат. Основное назначение АЛУ заключается в приеме данных, хранящихся в памяти, и осуществление над ними арифметических и логических операций под действием устройства управления. Схема АЛУ содержит комбинационные логические устройства, генераторы логических функций, сумматоры и полусумматоры.

Примеры тестов

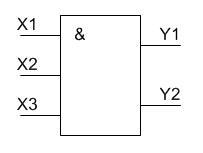

1. Число 110112 в десятичной системе исчисления 2.Число 111002 в десятичной системе исчисления 3.Число 1410 в двоичной системе исчисления 4.Число 1210 в двоичной системе исчисления 5. В двоичной системе исчисления сумма двух чисел 11012+1410 (пять бит) 6. В двоичной системе исчисления сумма двух чисел 11112+1510 (пять бит) 7.В двоичной системе исчисления сумма двух чисел 11112+1610 (пять бит) 8. В десятичной системе исчисления разность двух чисел 110102 - 001102 9. В десятичной системе исчисления разность двух чисел 110102 - 001112 10. Результат перемножения двух числе в двоичной системе исчисления 11112 и 210 (пять бит) 11. Результат перемножения двух числе в двоичной системе исчисления 11012 и 210 (пять бит) 12. Уровень сигнала на выходе Y1 при подаче на вход схемы сигналов с логическими уровнями

X1=1 X2=1 X3=1 13.Логический уровень сигнала на выходе Y1 при подаче на вход схемы сигналов с логическими уровнями

X1=0 X2=0 X3=1 14. Логический уровень сигнала на выходе Y2 при подаче на вход схемы сигналов с логическими уровнями

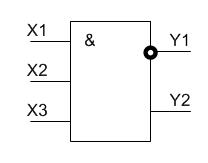

X1=1 X2=1 X3=1 -15. Логический уровень сигнала на выходе Y1 при подаче на вход схемы сигналов с логическими уровнями

X1=1 X2=1 X3=1 -16. Логический уровень сигнала на выходе Y1 при подаче на вход схемы сигналов с логическими уровнями

X1=0 X2=0 X3=1 17. Логический уровень сигнала на выходе Y1 при подаче на вход схемы сигналов с логическими уровнями

X1=1 X2=0 X3=1 17. Логический уровень сигнала на выходе Y1 при подаче на вход схемы сигналов с логическими уровнями, если выходные сигналы описаны уравнением:

X1=1 X2=1 X3=1 18. Логический уровень сигнала на выходе Y1 при подаче на вход схемы сигналов с логическими уровнями, если выходные сигналы описаны уравнением:

X1=0 X2=0 X3=1 19. Логический уровень сигнала на выходе Y1 при подаче на вход схемы сигналов с логическими уровнями, если выходные сигналы описаны уравнением:

X1=1 X2=0 X3=1 20. Логический уровень сигнала на выходе Y1 при подаче на вход схемы сигналов с логическими уровнями, если выходные сигналы описаны уравнением:

X1=1 X2=1 X3=1 21. Логический уровень сигнала на выходе Y1 при подаче на вход схемы сигналов с логическими уровнями, если выходные сигналы описаны уравнением:

X1=0 X2=0 X3=1 22. Логический уровень сигнала на выходе Y1 при подаче на вход схемы сигналов с логическими уровнями, если выходные сигналы описаны уравнением:

X1=1 X2=0 X3=1

Поиск по сайту: |