|

|

|

Архитектура Астрономия Аудит Биология Ботаника Бухгалтерский учёт Войное дело Генетика География Геология Дизайн Искусство История Кино Кулинария Культура Литература Математика Медицина Металлургия Мифология Музыка Психология Религия Спорт Строительство Техника Транспорт Туризм Усадьба Физика Фотография Химия Экология Электричество Электроника Энергетика |

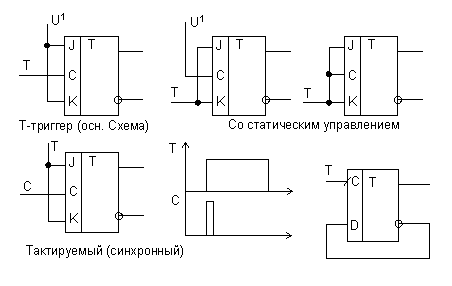

Способы управления триггерами

Способы управления, в зависимости от параметра синхронного входа сигнала, используемых для записи информации, триггеры бывают: 1. со статическим управлением записью (управление по уровню входного сигнала); 2. с динамическим управлением записью (по фронту или срезу); 3. двухступенчатое управление. Способ управления со статическим управлением записью имеет недостаток – триггер в период действия синхронного импульса ведет себя подобно асинхронному. Срабатывает в момент, когда входной сигнал достигает порогового уровня, то есть продолжает действие тактового импульса. Смена сигнала на информационный вход вызывает новое срабатывание. При динамическом управлении по фронту или по спаду тактового импульса триггер переключается только при переходе от 0 к 1, или от 1 к 0.

Возможность задержки момента опрокидывания триггера на время длительности тактового импульса позволяют по фронту производить считывание, а по срезу – запись информации.

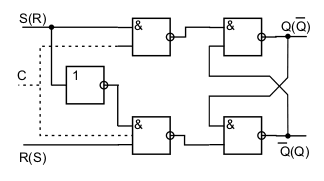

Двухступенчатые триггеры содержат две ячейки памяти, запись информации в которые происходит последовательно в различные моменты времени. Эту структуру называют «ведущий-ведомый» или MS-структура (Master-Slave). Первая ступень – промежуточная запись входной информации. Вторая ступень – последовательная запись и хранение. Формирование нового состояния происходит за два такта. Ввод информации в ведущую ступень происходит с приходом С1. Перезапись соответственно из ведущего в ведомый – с приходом С2, в это же время происходит обновление информации на Q или Управлять можно и одним тактовым импульсом. Запись в ведущую по фронту 0-1, перезапись в ведомую – по фронту 1-0. Динамические двухступенчатые триггеры называют флип-флоп. Статические – лэт. При низком уровне напряжения на входе С триггер находится в состоянии хранения информации (на выходах DD1 информация не может измениться, а значит и не меняется на выходах DD2). При поступлении «1» на вход С информация на выходах DD1 может измениться в соответствии с состоянием сигнала на информационных входах R и S. Однако триггер DD2 не может изменять информацию на входах, т.к. на его выходе «0». При окончании управляющего импульса DD1 не воспринимает информацию, т.к. информация с выходов переписывается к DD2. Асинхронные RS-триггеры

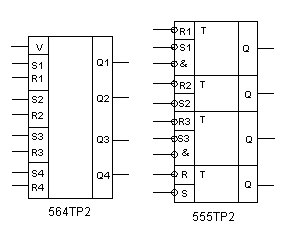

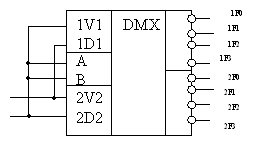

X – не имеет значения Вход V общий и управляет всеми (4) ключами. Когда вход V1 работает как S-триггер, на выходе будет тоже 1. Когда на V 0 – высокое импедансное состояние. Z – высокоимпедансное значение выхода (выход отключен от обеих шин источника питания и выходных клемм) Отсутствие запрещенного состояния обусловлено тем, что не введены выводы

Достоинство: нет неопределенного состояния, т.к. выходы прямые.

Синхронные RS-триггеры

При С = 0 на выходах DD2 и DD1 логическая «1» и RS-триггер на DD3 и DD4 находится в состоянии хранения информации (и не реагирует на изменение R и S). При С = 1, информация на управляющих входах RS-триггера зависит от состояния входа R и S, проинвертированных DD2 и DD1. Входы Sa¯ и Ra¯ предназначены для асинхронной установки триггера в заданное состояние. Двухступенчатые RS-триггеры

При высоком уровне на входе С происходит запись в ведущий RS-триггер на DD1 – DD4. Ведомый триггер на DD6 – DD9 блокирован низким уровнем с выходом DD5. При низком уровне на входе С блокируется ведущий триггер (переходит в состояние хранения информации). Высокий уровень с выхода DD5 разрешает перезапись с выхода ведущего на вход ведомого.

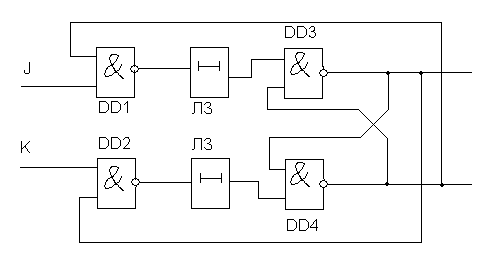

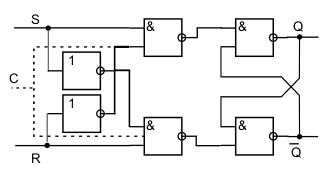

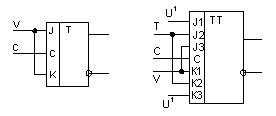

JK-триггеры

JK-триггеры не имеют неопределенных состояний. При всех входных комбинациях, кроме J = K = 1, они действуют подобно RS-триггеру. Причем J играет роль S, а К=R. При J=K=1 в каждом такте происходит опрокидывание триггера и выходные сигналы меняют свое значение. JK-триггеры относятся к универсальным устройствам (регистры, счетчики, делители), но кроме того, путем определенных соединений выводов, легко преобразуются в триггеры других типов. По схеме JK-триггеры отличаются от RS-триггеров наличием обратной связи с выхода на вход, поэтому состояние JK-триггера зависит не только от сигналов на входах J и K, но и от логической связи с ними сигнала с выходов Q и Q¯. Элементы временной задержки играют роль стабилизированного состояния триггера и на его функциональные свойства не влияют. Назначение – создание временного сдвига между моментом ввода входной информации JnQn¯ или KnQn и начала выхода Qn+1 и Qn+1¯. Без этих цепей во время действия комбинации Jn = Kn = 1 началась бы генерация для предотвращения которой задержка должна быть превыше длительности тактирующих импульсов. Действие JK-триггера: Qn+1 = Jn Qn¯VKn¯Qn.

RS-триггер ( в скобках R-триггер)

Е-триггер

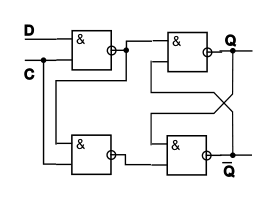

D-триггеры

p xIp7NSB9sGo0j9Z0X/uTlzDzr7MtD66/24nCVrtYPuWXDylvb6btA7Bspvxnhl98QoeWmI7hhDox J2EpKnLSvaRJelmtC2BHEu6LFfC24f8btD8AAAD//wMAUEsBAi0AFAAGAAgAAAAhALaDOJL+AAAA 4QEAABMAAAAAAAAAAAAAAAAAAAAAAFtDb250ZW50X1R5cGVzXS54bWxQSwECLQAUAAYACAAAACEA OP0h/9YAAACUAQAACwAAAAAAAAAAAAAAAAAvAQAAX3JlbHMvLnJlbHNQSwECLQAUAAYACAAAACEA Ljs0ZRYIAADPawAADgAAAAAAAAAAAAAAAAAuAgAAZHJzL2Uyb0RvYy54bWxQSwECLQAUAAYACAAA ACEACXhotN8AAAAJAQAADwAAAAAAAAAAAAAAAABwCgAAZHJzL2Rvd25yZXYueG1sUEsFBgAAAAAE AAQA8wAAAHwLAAAAAA== ">

Один установочный и синхронизирующий входы. На входе Q в такте n+1 повторяет входной сигнал Qn в предыдущем такте и сохраняет это состояние до следующего тактового импульса. D–триггеры имеют только один информационный вход. Сигнал на выходе Q в такте n+1 повторяет входной сигнал Dn в предыдущем такте n и сохраняет это состояние до следующего тактирующего импульса, то есть осуществляется задержка на один такт информации, существующей на входе D (Delay). Qn+1 = Dn

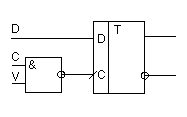

DV-триггеры

У DV-триггера разрешающий уровень появляется до сигнала. Если V = 1, то триггер функционирует как D-триггер, при V = 0 – переходит в режим хранения информации. Это расширяет функцию D-триггера, который не может хранить информацию более одного такта.

T- и TV-триггеры

TV1 – двухтактный JK – триггер с тремя J- входами и три входа К и все эти входы соединены по «и»:

TV11 – общие входы С и R, сдвоенный JK – триггер. TV15 - сдвоенный JK - триггер, срабатывает по заднему фронту, вход

T-триггер – счетный триггер, который имеет один информационный вход и меняет свое состояние всякий раз, когда меняет свое значение входной сигнал. В зависимости от того, фронт или срез используется для управления, считается, что триггер имеет прямой или инверсный вход. Единственный вид триггера, состояние которого определяется состоянием в предыдущем такте, а не от входной информации. Выполняет операцию сложения по модулю 2. Легко получается из D- или JK-триггера.

TV-триггер Сихронный TV-триггер

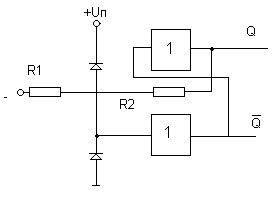

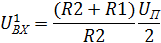

Триггер Шмидта на логических элементах

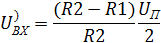

Обычно R1=300, R2=(2.2 ÷ 3.3)k. Нужен для ускорения сигнала.

ТЛ2 – шесть двухвходовых ТЛ3 (ТЛ1 654 серии) – четыре двухвходовых ТТЛ нужен для обработки медленно изменяющихся и зашумленных входных сигналах с целью исключения ложных срабатываний.

РЕГИСТРЫ Регистры – функциональные узлы, предназначенные для приема, хранения, передачи и преобразования информации. Используются в качестве управляющих и запоминающих устройств, генераторов и преобразователей кодов, счетчиков и делителей частоты, узлов временной задержки. Строятся на синхронных триггерах с динамическим или статическим управлением. Занесение информации в регистр называется операцией ввода или записью. Выдача информации к внешним устройствам характеризует операцию вывода или считывание. Запись информации в регистр не требует его предварительного обнуления. Регистры в зависимости от функциональных свойств подразделяются: - сдвигающие - накопительные (памяти, хранения) - универсальные. Регистры памяти

Предназначены для хранения двоичной информации небольшого объема в течение короткого промежутка времени. Представляют собой набор синхронных триггеров, каждый из которых хранит один разряд двоичного числа. Ввод и вывод информации производится одновременно во всех разрядах параллельного кода. Ввод обеспечивается тактовым командным импульсом. Считывание может производиться в прямом и обратном коде (с инверсных выходов). Регистры сдвига Помимо операции хранения осуществляют преобразование последовательного двоичного кода в параллельный, параллельного – в последовательный, а также арифметические и логические операции. Сущность сдвига – с приходом каждого тактового импульса происходит перезапись (сдвиг) содержимого триггера каждого разряда в соседний разряд без изменения порядка следования «0» и «1». При сдвиге вправо бит из более старшего разряда сдвигается в младший. При сдвиге влево – наоборот. Сдвигающие регистры классифицируются: 1. по способу ввода и вывода информации: - параллельные; - последовательные; - комбинированные (параллельно-последовательные, последовательно-параллельные). 2. по направлению передачи или сдвига информации: - однонаправленные; - реверсивные (обозначаются: RG ←, → и ↔ (влево, вправо и реверсивные)). Универсальные в зависимости от управляющих сигналов могут выполнять как операцию хранения, так и сдвиг. 4-х разрядный сдвигающий регистр с последовательным вводом на основе JK-триггеров

Допустим, что в регистр последовательно вводится начиная с младшего разряда двоичный код 1101, который поступает с внешнего устройства синхронно с тактовыми импульсами. С первым тактовым импульсом в триггер DD1 записывается «1» младшего разряда. Со следующим тактовым импульсом эта «1» будет сдвинута в триггер DD2 и окажется на его выходе. Одновременно в 1-ый триггер запишется «0». После 4-х тактовых импульсов параллельный код на выходах Q1—Q4 будет соответствовать последовательному входному. После пятого тактового импульса сигнал, бывший на выходах Q4, выводится из регистра и пропадает. После 8 тактов регистр полностью очищен от информации. Дополнительная логика позволяет вводить информацию в регистр параллельно, а снимать последовательно. Сдвигающийся регистр может быть использован в качестве кольцевого счетчика или счетчика Джонсона, который применяется для последовательного вывода информации без ее стирания.

Для этого информация с выхода многоразрядного регистра по цепи ОС снова вводится на вход. Пока на управляющем входе V единица, информация вводится в регистр по входу D и обратная связь не действует. За n тактов запоминается n разрядный код. Затем на V устанавливается «0» тактовыми импульсами по входу С. Информация с выхода Qn снова вводится в регистр одновременным последовательным (возможно и параллельным) считыванием и через n тактов находится в исходном состоянии. ИР-1

Он может выполнять следующие функции: - ввод информации параллельным кодом; - параллельный вывод через Q1-Q4; - последовательный вывод через Q1 либо Q4; - ввод информации последовательным кодом со сдвигом влево (обратное направление через D4); - ввод информации последовательным кодом со сдвигом вправо; - хранение. Регистр имеет: - 2 тактовых входа С1 и С2. - управляющий вход выбора режима V2 - 5 информационных входов (V1 для ввода в последовательном коде, D1-D4 для записи в параллельном коде) - 4 выхода Q1-Q4. Ввод информации параллельным кодом осуществляется при V2=1 и C2=0. Сдвиг информации в триггерах происходит по перепаду 1-0 на С2. Входы V1 и C1 при этом блокированы. В этом же режиме по входам V2, С2 производится преобразование последовательного кода в параллельный со сдвигом влево. В этом случае поток информации происходит в обратном направлении. Для этого соединяют Q4 – D3, Q3 – D2, Q2 – D1. Информация подается на D4. Сдвиг влево по перепаду 1-0 на С2.

Во избежание сбоев при смене состояний V2 должна происходить при C1=C2=0. Ввод информации последовательным кодом: входная информация подается на V1, а тактовые импульсы на С1. Сдвиг вправо происходит при каждом перепаде 1à0 тактовых импульсов.

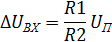

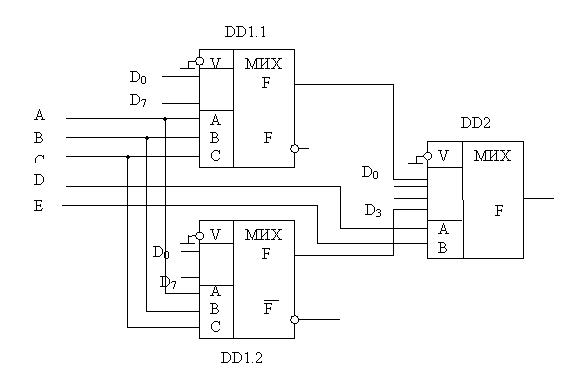

МУЛЬТИПЛЕКСОРЫ. ДЕМУЛЬТИПЛЕКСОРЫ И ДЕШИФРАТОРЫ Мультиплексоры –полупроводниковые приборы, которые коммутируют входную информацию, поступающую на разные входные шины на одну выходную в соответствии с информацией на адресном входе.

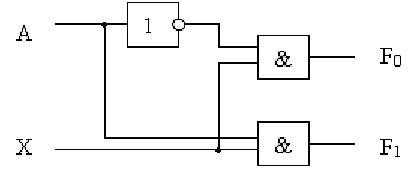

Мультиплексоры 2:1: 2-2и-2или

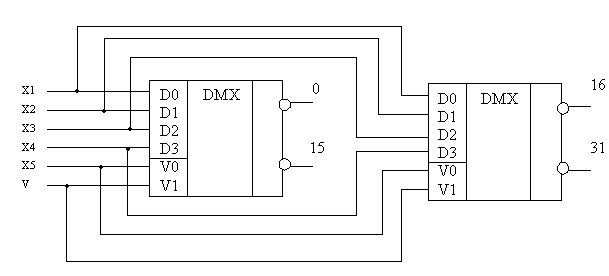

Если адресных входов (А) – n, то информационных входов (D) – 2n. Может одновременно присутствовать и стробирующий вход управлений всеми информационными входами.

Мультиплексор 4:1: увеличение разрядности – пирамидальное наращивание;

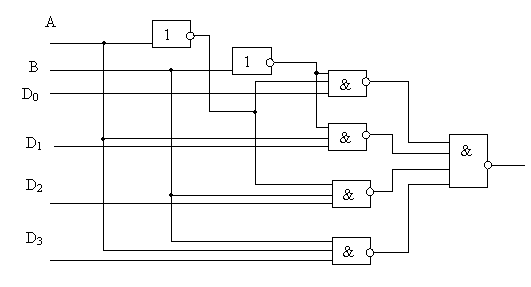

Для увеличения разрядности: DD1 – КП7 (8:1) DD2 - ½КП2

D и E – дополнительные коды, которые позволяют выделить какой0то из мультиплексоров, т.е. пропустить его информацию на выход.

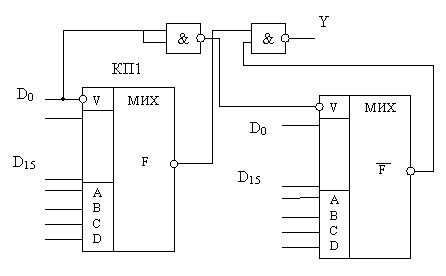

КП1 – 16:1 со стробирующим входом. КП2 – это 2 отдельных мультиплексора с общими входами.

- Зависимые с общим адресом.

Из этого мультиплексора можно получить 2 независимых:

КП5 – без стробирования.

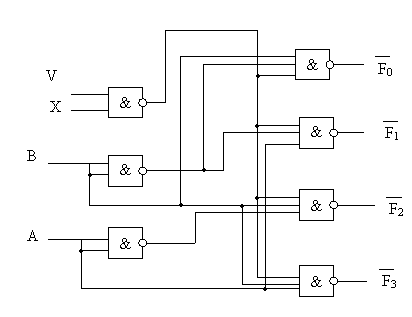

Демультиплексоры и дешифраторы Демультиплексоры противоположны мультиплексорам. У демультиплексоров сигнал с одного входа распространяется на один из выходов с соответствии с информацией адресного входа. 1:2

1:4

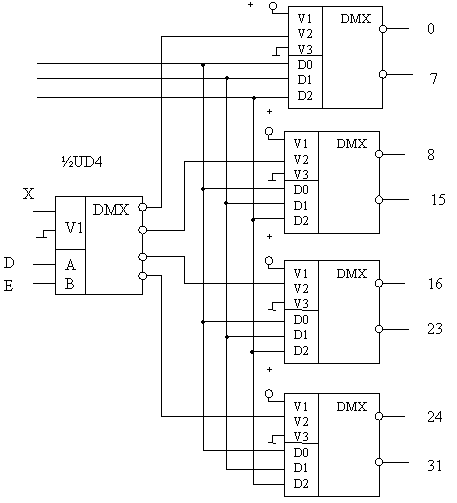

Дешифратор –устройство с несколькими входами и выходами, у которого определенные комбинации входных сигналов соответствует активное состояние одного или нескольких выходов. Увеличение разрядности дешифраторов: UD7

UD3

UD4 – сдвоенный дешифратор – демультиплексор с объединенными адресными входами.

Шифраторы являются преобразователями позиционного кода в двоичный. Чтобы устранить неоднозначность при появлении двух «1» на входах, назначается приоритет (более высокий у старшего разряда).

Счетчики импульсов. Двоичные счетчики и счетчики с произвольным коэффициентом счета. Принцип действия, структурные и принципиальные схемы, временные диаграммы работы счетчиков, их основные параметры. Разновидности счетчиков, особенности использования счетчиков при создании цифровых систем управления

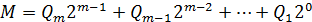

Счетчиком называется устройство, сигналы на выходе которого в определенном коде отображают число импульсов, поступивших на счетный вход. Триггер Т-типа может служить примером простейшего счетчика, считающего до двух. Счетчик, образованный цепочкой из m триггеров может подсчитать в двоичном коде Информация может сниматься с прямых и инверсных выходов триггеров. Когда число входных импульсов Коэффициент счета называют коэффициентом деления, следовательно каждый счетчик может использоваться как делитель частоты. Обозначения: СТ 2 – двоичный СТ10 – двоично-десятичный СТ2/10 – переключающийся Основные параметры: 1. Емкость. Емкость численно равна коэффициенту счета и характеризует число импульсов, доступных счету за 1 цикл. 2. Быстродействие определяется двумя параметрами: - под разрешающей способностью понимается минимальное время между двумя сигналами, при которых еще не возникают сбои в работе tразр.сч. - временем установки кода tуст равно времени между моментом поступления входного сигнала и переходом счетчика в новое состояние. Счетчики классифицируются следующим образом: 1. по модулю счета: - двоичные - двоично-десятичные - с произвольным фиксированным модулем счета - с переменным модулем 2. по направлению счета: - суммирующие - вычитающие - реверсивные 3. по способу организации внутренних связей - с последовательным переносом (асинхронные) - с параллельным переносом (синхронные) - с комбинированным переносом - кольцевые Классификационные признаки независимы и могут встречаться в разных комбинациях. Число, записанное в счетчик, определяется по формуле:

где m – номер триггера, Q – может принимать значение «1» и «0»,

Введением дополнительных логических связей (обратных и прямых) счетчики могут быть обращены в недвоичные, для которых

Счетчики с последовательным переносом представляют собой цепочку триггеров, в которых импульсы, подлежащие счету, поступают на вход 1-го триггера, а сигнал переноса передается последовательно от одного разряда к другому. Достоинства: простота схемы и увеличение разрядности. Недостатки: низкое быстродействие из-за последовательного принципа работы.

Поиск по сайту: |

.

.

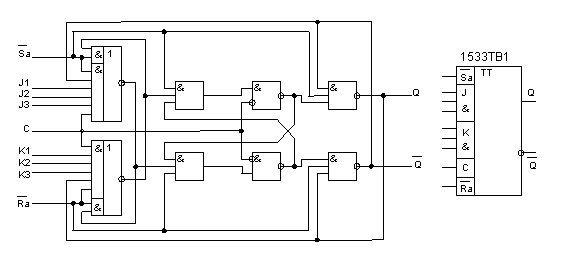

Триггер организован по принципу ведущий-ведомый и имеет по 3 входа J и K, связанных операцией &, синхронный вход С, а также асинхронные входы

Триггер организован по принципу ведущий-ведомый и имеет по 3 входа J и K, связанных операцией &, синхронный вход С, а также асинхронные входы  и

и  для установки триггера в состояние «0» и «1» независимо от сигналов информационных и тактовых входов. У ТВ6 отсутствует вход

для установки триггера в состояние «0» и «1» независимо от сигналов информационных и тактовых входов. У ТВ6 отсутствует вход  , у ТВ10 отсутствует вход

, у ТВ10 отсутствует вход  . У ТВ11 объединены входы С и

. У ТВ11 объединены входы С и  , что позволяет преобразовывать эти триггеры путем объединения J и

, что позволяет преобразовывать эти триггеры путем объединения J и

K3

R

K3

R

( не К), что позволяет его легко преобразовать в D - триггер.

( не К), что позволяет его легко преобразовать в D - триггер.

Пороги срабатывания и ширину петли гистерезиса можно в некоторых пределах регулировать.

Пороги срабатывания и ширину петли гистерезиса можно в некоторых пределах регулировать.

50)k

50)k

500)

500)

импульсов в двоичном коде. Каждый из триггеров называется разрядом счетчика. Число

импульсов в двоичном коде. Каждый из триггеров называется разрядом счетчика. Число  называется коэффициентом или модулем счета.

называется коэффициентом или модулем счета. , то при n входа равном Kсч происходит переполнение, счетчик возвращается в нулевое состояние и повторяет цикл. Каждый разряд счетчика делит частоту входных импульсов пополам. Для периодических сигналов

, то при n входа равном Kсч происходит переполнение, счетчик возвращается в нулевое состояние и повторяет цикл. Каждый разряд счетчика делит частоту входных импульсов пополам. Для периодических сигналов  .

.

– вес младшего разряда.

– вес младшего разряда. . Например, двоично-десятичные с Ксч=10 (двоичный по коду счета, десятичный по числу состояний). Организуется из 4-х разрядных двоичных путем исключения избыточных состояний за счет введения дополнительных связей. Когда счетчик используется в качестве делителя, направление счета роли не играет.

. Например, двоично-десятичные с Ксч=10 (двоичный по коду счета, десятичный по числу состояний). Организуется из 4-х разрядных двоичных путем исключения избыточных состояний за счет введения дополнительных связей. Когда счетчик используется в качестве делителя, направление счета роли не играет.