|

|

|

Архитектура Астрономия Аудит Биология Ботаника Бухгалтерский учёт Войное дело Генетика География Геология Дизайн Искусство История Кино Кулинария Культура Литература Математика Медицина Металлургия Мифология Музыка Психология Религия Спорт Строительство Техника Транспорт Туризм Усадьба Физика Фотография Химия Экология Электричество Электроника Энергетика |

Мультивибратор с регулируемой скважностьюСтр 1 из 3Следующая ⇒

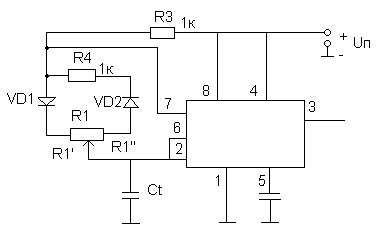

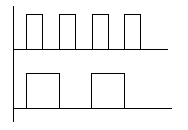

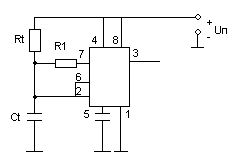

Заряд Ct: +Uп – R3 – VD1 – R1’ – Ct; разряд: Ct – R1’’ – VD2 – R4 – 7. Изменяя положение подвижного контакта R1, можем в широких пределах менять скважность, оставляя при этом частоту неизменной, т. к. R1’+R1’’=R1=const.

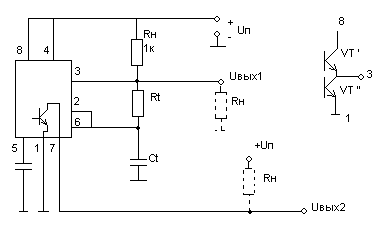

Генераторы меандра 1)

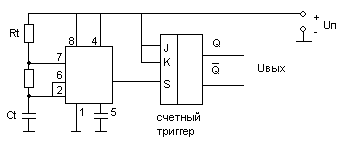

В J-K триггерах J соответствует S, а K – R. При J=K=1 – запрещенное состояние -

Недостаток: малый выходной ток.

2)

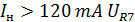

Заряд Ct: Uп – VT’ – Rt – Ct. Разряд Ct: Ct – Rt – 3 – VT’’. Недостаток: можно коммутировать только нагрузку, подключенную к источнику питания. 3)

При включении питания Недостаток: усложнение схемы. 4)

Заряд Ct осуществляется по цепи: +Uп – Rt – Ct. Разряд: Ct – R1 – 7. Одновременно с разрядом протекает ток заряда через Rt. Недостаток: необходимость точного подбора Rt и R1 и ограничение в их выборе. Импульсный стабилизатор напряжения (ключевой стабилизатор на таймере)

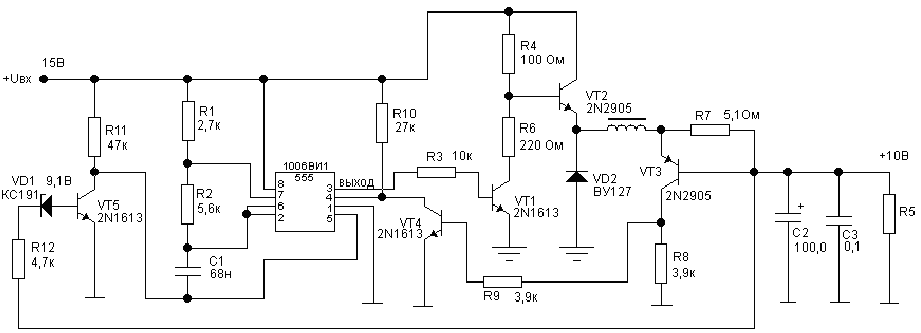

Таймер вырабатывает прямоугольные импульсы заданной длительности. Длительность зависит от величины Uвых. Таймер DA обеспечивает формирование прямоугольных управляющих импульсов, которые с вывода 3 попадают на базу VT1, из коллектора VT1 усиленные – на базу ключевого VT2, работающего в понижающем преобразователе. Как только напряжение на выходе приближается к 10В (UVD1+UБЭVT5=9,1+0,6), VT5 приоткрывается и уменьшает длительность управляющих импульсов вплоть до полного прекращения. Частота и скважность импульсов зависят от R1,R2, C1 и величины напряжения на 5-ом выводе

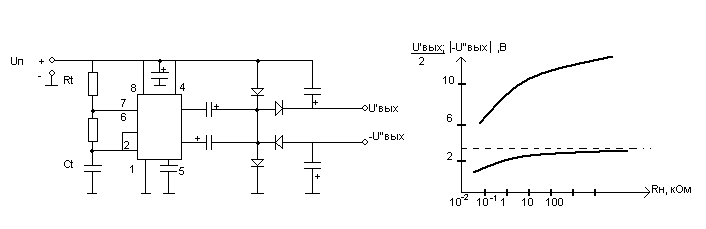

Диодные емкостные преобразователи

Схемы на таймере: - преобразователь напряжение-частота; - преобразователь напряжение – длительность импульса; - преобразователь температура – частота; - преобразователь сопротивление – длительность импульса; - аналоговый делитель напряжений; - компараторы, в том числе с регулируемым гистерезисом; - триггеры Шмидта с регулируемым и постоянным порогом срабатывания; - мощные кабельные усилители; - мощные логические элементы; - генераторы, управляемые напряжением; - реле времени; - ШИМ-генераторы;

МОДУЛЯЦИЯ Модуляция – изменение одного из параметров сигнала несущей частоты по закону модулирующего сигнала. Изменяемые параметры: - амплитуда - частота и фаза - относительная ширина импульса. Необходима для передачи нескольких независимых сообщений по одному каналу связи без взаимного влияния друг на друга.

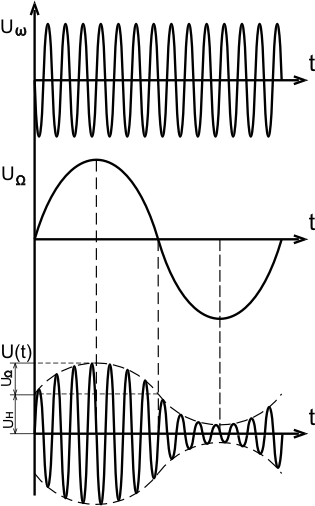

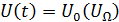

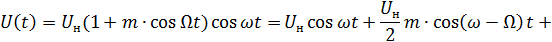

Виды модуляции 1) Амплитудная модуляция Осуществляется путем перемножения полезного сигнала и сигнала несущей частоты, в результате чего амплитуда высокочастотных колебаний изменяется по закону передаваемого смыслового сигнала.

Амплитудная модуляция применяется на длинных (ДВ), средних (СВ) и коротких волнах (КВ). Расстояние между станциями 9 кГц. Чем уже полоса занимаемых частот, тем легче при одинаковой мощности передатчика обеспечить дальность или во столько же раз уменьшить шумы.

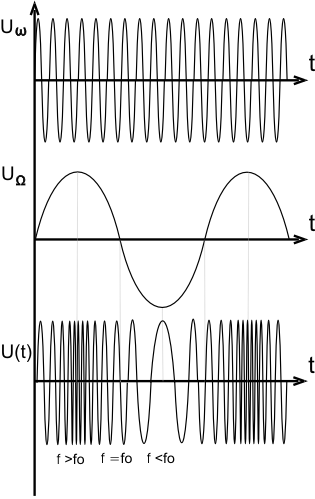

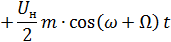

2) Частотная и фазовая модуляция.

Видно, что чем больше амплитуда, тем больше частота.

Разложение в ряд Фурье:

Если ограничиваться составляющими, которые обладают более чем 3% энергии несущей, то в практический спектр войдут кроме несущей только 2 боковые гармоники. В этом случае спектр имеет ту же ширину, что и спектр АМ-колебаний (узкополосная частотная модуляция). При β>1 спектр определяется Применение: из-за большой помехоустойчивости линии связи основное применение находит ЧМ. Фазовая модуляция используется как промежуточный вид для получения ЧМ. Достоинства: высокая защищенность от помех при воздействии атмосферных и промышленных помех. Недостатки: относительно широкая полоса занимаемых частот (≥150 кГц), относительная сложность модуляции и демодуляции.

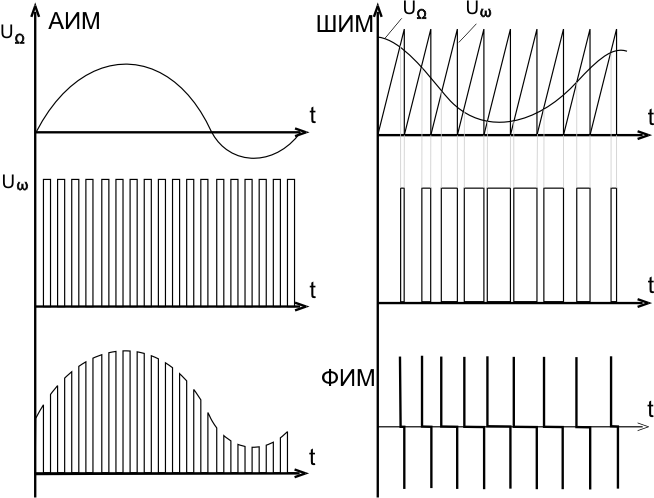

3) Импульсная модуляция В зависимости от того, какой из параметров импульсной последовательности изменяется в процессе модуляции, различают виды модуляции: - Амплитудно-импульсная –– АИМ - Широтно- импульсная –– ШИМ - Фазо-импульсная –– ФИМ - Частотно-импульсная –– ЧИМ - Кодо-импульсная –– КИМ

Модуляция импульсов по фазе состоит в изменении временного положения импульсов относительно опорных или тактовых точек и получается путем дифференцирования ШИМ. Применение: наиболее часто импульсная модуляция используется в многоканальной радиосвязи и телеметрии. ШИМ используется в импульсных стабилизаторах и преобразователях напряжения, в схемах управления электродвигателем. ШУМЫ И ПОМЕХИ Шумами принято называть некий сигнал, маскирующий полезный, чаще всего случайный шум физической природы. Например, тепловой шум. Шум характеризуется частотным спектром, распределением амплитуд, источником. Помеха – паразитные сигналы от других источников и наводки, мешающие приему. Например, грозовые разряды, радио- и телепередающие станции, лифты, метро, выключатели, электродвигатели.

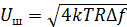

Тепловой шум (шум Джонсона) Любой резистор генерирует на своих концах некоторый шум напряжения с горизонтальным частотным спектром, т.е. одинаковая мощность шума на всех частотах (белый шум, т.е. энергетическая плотность мощности шума не зависит от частоты).

k - постоянная Больцмана; Т - абсолютная температура, К; R – сопротивление; Например, резистор с R=10 кОм, при комнатной температуре T=293° К в полосе пропускания

Для уменьшения теплового шума можно уменьшать температуру, сопротивление, полосу частот. Значение шума Джонсона состоит в том, что он устанавливает нижнюю границу напряжения шумов любого детектора, источника сигналов или усилителя, имеющего ненулевое выходное сопротивление.

Дробовой шум (шум Шотки)

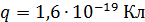

Электрический ток представляет собой движение дискретных зарядов, а не плавное непрерывное течение. Конечность заряда приводит к статическим флуктуациям тока.

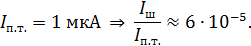

Уменьшать дробовой шум можно уменьшением полосы частот При больших токах

Фликкер-шум (шум 1/f)

Дробовой и тепловой шумы – это неуменьшаемые в данных условиях виды шума, происходящие вследствие действия физических законов. Избыточные виды шума зависят от конструкции и материала резистора. Пример: 0,1-3 мкВ – для углеродно-композитных резисторов; 0,05-0,3 мкВ – для углеродно-пленочных; 0,02-0,2 мкВ – для металлопленочных; 0,01-0,2 мкВ – для проволочных. Шум имеет спектр 1/f (постоянная мощность на декаду частоты), его амплитуда экспоненциально уменьшается с уменьшением частоты, иногда его называют «розовый шум».

Помехи Помехи наводятся техногенными факторами.

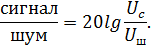

Коэффициент шума:

Шум тока и напряжения транзисторных усилителей При низком сопротивлении источника сигналов (200 Ом-1 Мом) главную роль играет шум напряжения, т.к. шум тока вызывает дополнительное напряжение, равное:

В этом случае целесообразнее использовать малошумящие биполярные транзисторы. При больших сопротивлениях источника (200 Ом – 0,1 Мом) преобладает шум тока транзисторов, поэтому лучшим устройством для усиления с малыми шумами будет полевой транзистор ПТ. При сопротивлениях При Помехи проникают на вход усилителя через емкостную связь. При этом чем выше входное сопротивление усилителя, тем более восприимчив он к таким помехам. Статистическую помеху можно практически полностью устранить экранировкой входа усилителя высокопроводящим материалом (алюминий, медь, серебро). При этом создается эквипотенциальная поверхность. Магнитная связь

Магнитная связь создается за счет возникновения магнитного поля при протекании тока через проводник. Это поле наводит паразитные токи во входных чувствительных цепях. Магнитное поле можно лишь ослабить экранировкой ферромагнитным материалом с высокой электромагнитной проницаемостью (пермаллой). Наиболее подвержены этим помехам низкоомные входные цепи. Способы борьбы с помехами: - использование витых пар для передачи сигналов; - стремление к отсутствию замкнутых контуров, особенно в шинах питания и земли; - правильное заземление. Оно должно быть не последовательным, а параллельным.

СОВРЕМЕННЫЕ ИНТЕГРАЛЬНЫЕ МИРОВЫЕ МИКРОСХЕМЫ

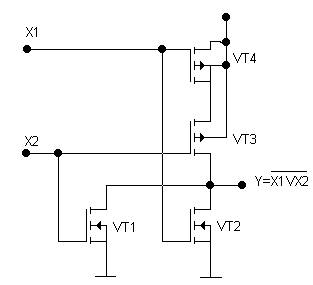

В качестве основных активных элементов могут использоваться: - биполярные транзисторы; - полевые МДП транзисторы и структуры. Способ соединения транзисторов между собой в пределах одного элемента определяет их логику.

Основные типы логики на БПТ Устаревшие: - РТЛ (резисторно-транзисторная логика) - ДТЛ (диодно-транзисторная) Современные: - ТТЛ (транзисторно-транзисторная логика) - ТТЛШ (транзисторно-транзисторная с транзисторами Шоттки) - ЭСЛ (эмиттерносвязанная логика) - И2Л (инжекционная, ИИЛ – инжекционно-интегральная) Среди МОП-логики: - n-МОП (МДП) - p-МОП - КМОП - КМОП с параметрами ТТЛ (самая современная логика). Пример: НС, АС – зарубежная, 1564, 1554 – отечественные аналоги). Разновидности функциональных схем

Логические элементы представляют только небольшую часть устройств обработки и преобразования двоичной информации. В общем случае можно выделить 2 класса: - комбинационные схемы - последовательные устройства Комбинационные схемы характеризуются отсутствием памяти (память – свойство системы сохранять в течении требуемого времени значение сигнала, характеризующее внутреннее состояние цифрового устройства). Сигнал на выходах комбинационного устройства в любой момент времени однозначно определяется сочетанием сигналов на входах и не зависит от его предыдущих состояний. Схемным признаком таких схем является осуществление в цепи обратной связи. Примеры: логические элементы, эл. ключи, шифраторы, дешифраторы, мультиплексоры, демультиплексоры, большинство арифметических устройств. Последовательные схемы обладают памятью. При смене информации на входах для предсказания сигнала на выходах необходимо знать и состояние, в котором устройство было до этого. В этих устройствах, как правило, есть цепи обратной связи. Простейшие из них – триггеры, счетчики, регистры, запоминающие устройства. Обновление информации на выходах происходит в момент начала нового цикла. Предыдущее состояние обозначается Тn, последующее – Тn+1. Основные параметры логических микросхем (интегральные параметры)

1. Надежность характеризуется тремя взаимосвязанными параметрами: - интенсивность отказов λ; - наработкой на отказ Т; - вероятность безотказной работы Р (T) в течение заданного времени t. Различают отказы соединений и отказы элементов. 2. Стойкость к механическим и климатическим воздействиям – вибрация, удары, центробежные силы, воздействиям атмосферы и т.д. Температурный диапазон: 0 ÷ +70ºС (микросхемы широкого применения); -60 ÷ +125ºС (микросхемы специального назначения). Влажность до 98 %. 3. Быстродействие – прямо пропорционально потребляемой мощности. 4. Мощность рассеивания. 5. Нагрузочная способность – при исполнении микросхем разных серий количество входов будет различным. Оно может быть указано в таблице, либо рассчитано по входным и выходным токам. 6. Помехоустойчивость определяется типом логики и уровнем логической «1» и «0». - статическая; - динамическая; - по низкому уровню; - по высокому уровню.

Динамическая помехоустойчивость КПОМ ниже. 7. Степень интеграции характеризует достигнутый уровень технологий, определяется числом простейших эквивалентных логических элементов (типа 2И) на кристалле. Больше 10 тыс – сверхбольшая степень интеграции. 8. Затухание переходных процессов за время одного такта.

Особенности применения элементов ТТЛ

В зависимости от серии при соединении друг с другом разные серии могут обладать различной нагрузочной способностью. Для элементов своих серий нагрузочная способность =10, повышенная =30. Объединять входы с целью увеличения мощности можно только для логических элементов в одном корпусе. Объединять входы можно, но увеличивается нагрузка и входная емкость. Входы всех элементов ТТЛ должны быть подключены либо к выходам предыдущих элементов, либо к источнику сигнала логической «1» либо «0». Неиспользуемые выходы могут не подключаться. На землю либо питание не включать! Неподключенный вход ТТЛ имеет уровень логической «1», но обладает низкой помехоустойчивостью. Емкость нагрузки должна быть ограничена максимальным значением, который указывается в справочнике.

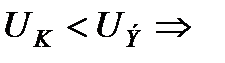

Элементы на основе ТТЛ

В основе – многоэммитерный транзистор. Серия 155. Если на всех входах «1» , то на коллекторе Если на любом из входов «0», то VT1 переключается из инверсного в активный режим и отпирается. В этом случае напряжение на его коллекторе (0,8В) уже недостаточно для отпирания VT4 и VT5. VT4 при этом открыт и на выходе появляется логическая единица. R5 предназначен для защиты выходов при кратковременном замыкании на землю.

Серия повышенного быстродействия. VT1, VT2 – VT5 – используются транзисторы Шоттке.

Следующим шагом к повышению быстродействия стало использование транзистора Шотке.

У диода Шотке напряжение отпирания 0,3-0,4 В. Напряжение на базе транзистора Шотке не может превышать напряжение на его коллекторе более, чем на 0,4 В, т.е. коллекторный переход никогда полностью не открывается транзистор не заходит в режим насыщения, что резко увеличивает его быстродействие.

Каскад с открытым коллектором

Обычная нагрузочная способность равна 10 входам, которые можно подключить к одному входу. Повышенная нагрузочная способность = 30. В логических элементах входы должны быть обязательно к чему-нибудь подключены. Если схема «И» – вход подключить к «1». Если «ИЛИ» – подать «0».

В схемах с общим коллектором неиспользуемые входы могут оставаться неподключенными. Выходы двух обычных элементов объединять нельзя, за исключением находящихся в одном корпусе с целью увеличения выходной мощности. В схемах с общим коллектором можно объединять выходы и делать монтажные ИЛИ. Недостаток: малый ток высокого уровня, ограниченный коллекторным резистором.

Расширение по «И»

См. на рисунках дополнительные входы.

2И-2ИЛИ-НЕ

К и Э предназначены для расширения по ИЛИ.

Расширитель по ИЛИ

Существуют элементы с открытым коллектором, допускающие подачу повышенного напряжения (15-30 В) через резистор на коллектор выходного транзистора, что позволяет коммутировать различную нагрузку.

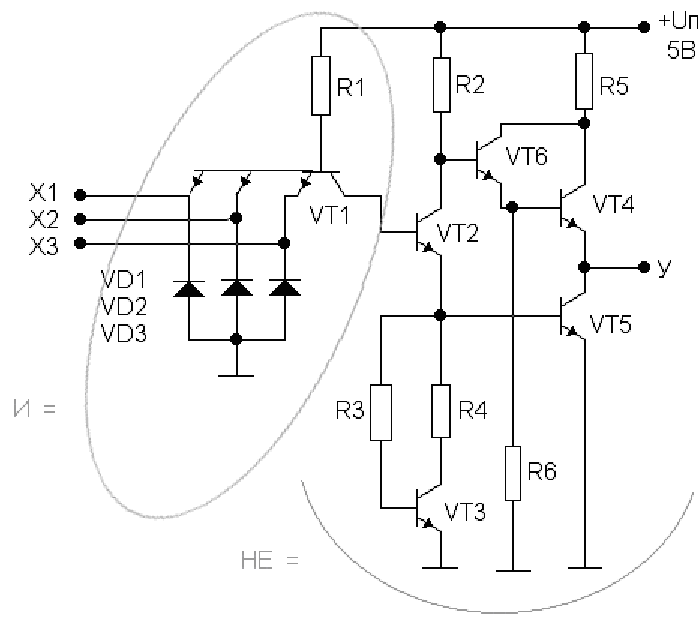

Логический элемент с тремя выходными состояниями (Z-состояние)

Когда VT3 заперт и когда на EZ подали сигнал низкого уровня, VT2 и VT3 – заперты, VT1 открыт, схема действует по обычному алгоритму 2И-НЕ. VD1 также закрыт, смещен в обратном направлении. При EZ=1 VT1 смещен в инверсном направлении, т.е. Uкб1 открыт, VT2, VT3, VD1 также открыты, т.е. UА®0. VT6 закрыт. VT5 также закрыт, поскольку UЭ4-3=0, VT4 открыт. Если закрыт VT5, то закрыт и VT7. Выходной вывод отсоединен от входных церей и обеих ШИМ питания. Это также уменьшает выпрямляемую элементом мощность.

Сравнительные характеристики серии логических микросхем

Элементы КМОП и ЭСЛ

Для элементов КМОП потребление указывается для статического режима, что справедливо для низких частот переключения. При максимально возможных частотах переключения мощность потребления КМОП-микросхем достигает, а часто и превышает потребление других серий ТТЛ, ТСЛ на этих частотах. При расчете источника питания необходимо учитывать потребление мощности на максимальной рабочей частоте, что можно извлечь из справочника. Eпотр = Pпотрtзд =>если tздуменьшить в nраз, то Pпотр увеличится в 2nраз.

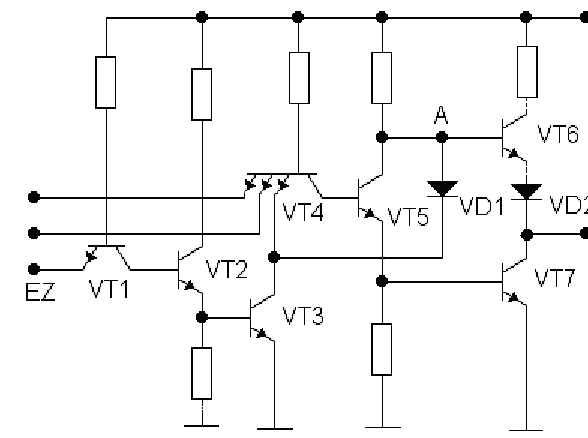

ЭСЛ – эмиттерно-связанная логика. Базовые элементы

В исходном состоянии VT4 и VT5 открыты, VT1 – VT3 закрыты; на коллекторе VT4, а значит на Y2 низкий уровень. На коллекторах VT1 – VT3 и на выходе Y1 – высокий. При подаче высокого уровня на любой из входов x соответствующий транзистор открывается, потенциал его коллектора и выхода Y1 становится низким, VT4 и VT5 запираются за счет повышения напряжения на Rэ , потенциал коллектора VT4 и выхода Y2 становится единичным. VD1 и VD2 предназначены для температурной компенсации VT4 и VT5. U0 = -0,7 ÷ -0,95 ≈ -0,8 U1 = -1,45 ÷ -1,95 ≈ -1,6 Достоинства: высокое быстродействие (1 нс) достигается тем, что транзисторы дифференциального каскада и другие не входят в режим насыщения, а также малой разницей между уровнем логического «0» и логической «1» (0,8В). Недостатки: небольшая помехоустойчивость из-за малой разницы уровня «1» и «0». Для согласования микросхем различных видов логики используются микросхемы преобразования уровня. Используются во входных высокочастотных каскадах.

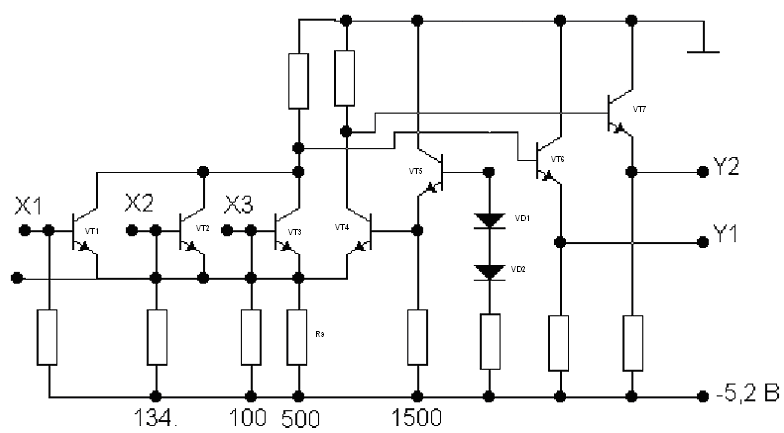

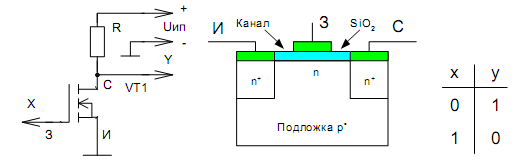

Базовые элементы КМОП

Стандартный КМОП допускает использование Uп от 5В до 15В. Быстродействие изменяется в три раза, возрастает и мощность. Это позволяет непосредственно соединить схемы КМОП и ОУ.

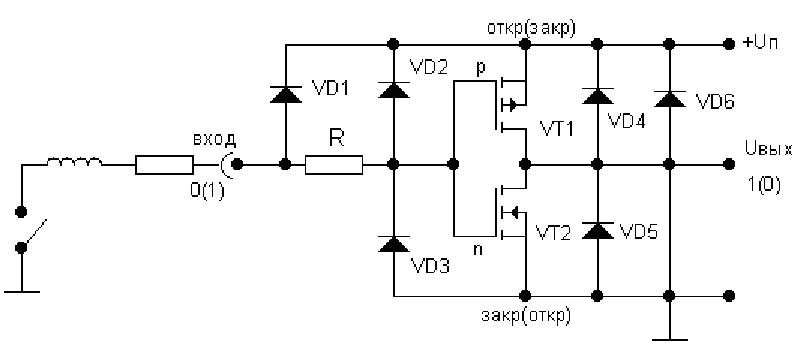

Двунаправленный ключ

При изменении входного сигнала сопротивление каналов транзистора с n и p каналом изменяется в противоположную сторону. Специальные схемные решения позволяют сделать эквивалентное сопротивление ключа независимым от величины и направления входного сигнала. Величина сопротивления канала ключа достигает единиц Ом. При отсутствии отпирающего напряжения на затворе сопротивление велико (десятки МОм), что равносильно разрыву цепи. Резистивный характер сопротивления канала позволяет использовать двунаправленные ключи не только для переключения логических сигналов, но и (в отличие от ТТЛ) для переключения аналоговых сигналов, а также для регулировки последних, используя ключ в этом случае в качестве переменного резистора, управляемого напряжением.

Инвертор КМОП

При высоком уровне напряжения ан входе VT2 открыт (UЗИ2»UП), VT1 закрыт (UЗИ1»0). На выходе нулевой уровень напряжения. При низком уровне VT1 и VT2 меняются ролями (VT2 закрыт, VT1 открыт). На выходе – «1». Диоды VD1-VD6 обязательно присутствуют во всех логических элементах КМОП, так как они защищают ПТ от статического электричества и возможных индуктивных отрицательных выбросов на выводах микросхемы. Они не изготавливаются специально, а получаются автоматически в технологическом процессе при изоляции транзисторов друг от друга. В инверторе VD3, VD5, VD6 защитные элементы от отрицательных импульсов. Диоды VD1, VD2, VD4 защищают вход и выход от положительных выбросов и ограничивают его на уровне Uп+0,6. Для дополнительной защиты входов, особенно при длинных входных проводах, и для устранения паразитных колебаний последовательно с входом включают резистор для ограничения тока заряда включения емкости. Отрицательное напряжение на выводах подключенной микросхемы не может превышать 1,2 В; положительное – (UП+0,6) В.

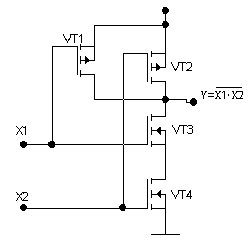

Схема И-НЕ

При логической «1» n-каналы VT3 и VT4 открыты, а p-канальные VT1 и VT2 – заперты, на входе логический «0». При подаче хотя бы одного логического «0» на вход, оказывается запертым одним из VT3 или VT4 и открытым хотя бы один из VT1 и VT2, что даст логическую «1» на выходе.

Схема ИЛИ-НЕ

При двух логических «0» входы VT1 и VT2 закрыты, а VT3 и VT4 открыты. На выходе – логическая «1». При логической «1» на любом из выходов по крайней мере один из n-каналов и хотя бы один из последовательных соединений p-каналов закрыт. На выходе 0.

Логические элементы с открытым стоком

H F1zfQRXcBFpt9Z79Qx7iscretD+MTjE+pL8myM6GEnhYAcMjnm47yVn7vGfr8/qeO0zy5FSTZxYX HeQOPUvUh9xbKnl1gvfCCR6AbpjhjTY6evG1Ax1C2PVhRt+exKxRp6U+KfUB6oZZ3Snexg51tm85 6h0Iu1JCo+5/jzr5sg940Yd83Ld5C4p4dUl/XT7nu3tXy9U/AAAA//8DAFBLAwQUAAYACAAAACEA xUwIL9sAAAAFAQAADwAAAGRycy9kb3ducmV2LnhtbEyPQUvDQBCF74L/YRnBm92kNFJiNkVKi1S8 2Hrxts2OSTA7G7KbZOuvd/Sil2Eeb3jzvWITbScmHHzrSEG6SEAgVc60VCt4O+3v1iB80GR05wgV XNDDpry+KnRu3EyvOB1DLTiEfK4VNCH0uZS+atBqv3A9EnsfbrA6sBxqaQY9c7jt5DJJ7qXVLfGH Rve4bbD6PI5WwZw87+LXaf8yvVOk1fR0GEOWKXV7Ex8fQASM4e8YfvAZHUpmOruRjBedAi4Sfid7 y1XK8sxLtk5BloX8T19+AwAA//8DAFBLAQItABQABgAIAAAAIQC2gziS/gAAAOEBAAATAAAAAAAA AAAAAAAAAAAAAABbQ29udGVudF9UeXBlc10ueG1sUEsBAi0AFAAGAAgAAAAhADj9If/WAAAAlAEA AAsAAAAAAAAAAAAAAAAALwEAAF9yZWxzLy5yZWxzUEsBAi0AFAAGAAgAAAAhAJz0VOKABgAA80UA AA4AAAAAAAAAAAAAAAAALgIAAGRycy9lMm9Eb2MueG1sUEsBAi0AFAAGAAgAAAAhAMVMCC/bAAAA BQEAAA8AAAAAAAAAAAAAAAAA2ggAAGRycy9kb3ducmV2LnhtbFBLBQYAAAAABAAEAPMAAADiCQAA AAA= ">

Не использованные входы КМОП надо включать так, чтоб не нарушались условия работы микросхемы в целом. В отличие от ТТЛ можно подключить к Uп напрямую. Нельзя оставлять неподключенными. При случайном соединении выхода с системой питания или с общей линией через открытие. Транзистор пропускает ток, ограниченный только сопротивлением канала и внутренним сопротивлением источника питания. Ток короткого замыкания и мощность рассеивания увеличиваются с ростом напряжения питания. При напряжении питания не более 5В и комнатной температуре 25˚С микросхема не выходит из строя при достаточно долговременном коротком замыкании. Достоинства: Очень низкое потребление энергии в режиме покоя и при невысокой частоте переключения. При частотах близких к граничным потери мощности возрастают из-за увеличение токов заряда емкостей затвор-канала. Широкий диапазон напряжения питания (5 – 15 В). Не боится к.з. на выходных шины питания и земли из-за конечного сопротивления канала (≠0). Недостатки: Боится статического электричества. Невысокое быстродействие.

ДВОИЧНЫЕ СУММАТОРЫ. ОДНОРАЗРЯДНЫЕ ДВОИЧНЫЕ СУММАТОРЫ. ПАРАЛЛЕЛЬНЫЕ МНОГОРАЗРЯДНЫЕ СУММАТОРЫ. СТРУКТУРНЫЕ СХЕМЫ, ОСОБЕННОСТИ РАБОТЫ. ОСНОВНЫЕ ПАРАМЕТРЫ

Сумматоры– функциональные узлы, выполняющие сложение чисел. Подразделяются на: - комбинационные (нет памяти) - накопительные Каждый из этих групп может быть последовательного и параллельного типа. Сложение чисел в последовательных сумматорах осуществляется поразрядно последовательно во времени. В сумматорах параллельного типа сложение всех разрядов многоразрядных чисел происходит одновременно. Как последовательные, так и параллельные сумматоры строятся на основе одноразрядных суммирующих схем. Сумматоры, выполненные в виде самостоятельных микросхем, являются комбинационными.

Состоит из двух полусумматоров: 1-й служит для сложения двух чисел, принадлежащих одному разряду, 2-й складывает промежуточную сумму с переносом. Входы можно менять местами. Последовательный сумматор

Достоинства: малые аппаратные затраты. Недостатки: низкое быстродействие.

Разработаны схемы более быстродействующих сумматоров, например: - n-разрядный параллельный сумматор с последовательным переносом. Быстродействие его ограничено задержкой переноса, т.к. формирование сигнала переноса на выходе старшего разряда не может произойти до тех пор, пока сигнал переноса младшего разряда не распространится последовательно по всей системе. - n-разрядный параллельный сумматор с параллельным переносом с использованием специальных узлов блоков сквозного переноса.

Сумматоры ТТЛ

Предназначен для построения многоразрядных схем сложения и вычитания с параллельной обработкой входной информации и последовательной передачей сигналов переноса. Для каждого слагаемого А и В имеется по 4 входа. Элементы входной логики объединены цепью монтажное &, поэтому сигналы на входы А3 и В3 должны поступать с устройств с открытыми коллекторами. Благодаря усложненной входной логике, сумматор обладает большими функциональными возможностями. Многоразрядные сумматоры и вычитатели на его основе организуются без дополнительных элементов и могут работать в положительной и отрицательной логике. Удобен для схем с последовательным суммированием. Прямые и инверсные входы принадлежащие каждому из слагаемых одновременно не используются. Когда в работе А1, А2, В1, В2 на А3, А4, В3, В4 подаем высокий уровень. При использовании в качестве рабочих А3, А4, В3, В4 на остальные подаем «0».

ИМ2 – двухразрядный полный сумматор. ИМ3 – четырехразрядный полный сумматор.

Действие основано на параллельном суммировании данных в разных разрядах при последовательном переносе из разряда в разряд. Вход переноса оставлять открытым нельзя.

Чтобы сделать из сумматора вычитатель нужно инвертировать одно из слагаемых.

Сумматор-вычитатель (сложение

Умножитель

Для умножения, в т.ч. чисел большей разрядности могут использоваться специальные микросхемы умножители. Деление аппаратными средствами сложнее других арифметических действий. Часто применяют методы основанные на последовательном вычитании делимого из делителя с помощью вычитателя.

ИМ5 – 2 одноразрядных двоичных полусумматора. ИМ6 – 4х-разрядный полусумматор с ускоренным переносом. ИМ7 – 4 одноразрядных последовательных тактируемых сумматора-вычитателя.

ТРИГГЕРЫ

Триггеры – класс устройств, общим свойством которых является способность длительно оставаться в одном из двух (или нескольких возможных) устойчивых состояний и скачком чередовать их под воздействием внешних сигналов. Одно из основных применений – запоминание информации. Под памятью триггера подразумевают способность оставаться в заданном состоянии и после прекращения действия переключающего сигнала. Приняв одно из состояний за «1», а другое за «0», можно считать, что триггер хранит или помнит один разряд двоичного числа.

Классификация триггеров

По количеству информационных входов: - с одним информационным входом: D-, T-триггеры; - с двумя информационными входами: RS, DV, JK, TV, S, R, E; - с тремя и более: По способу ввода информации:

Простейшая триггерная ячейка может быть сделана на элементах ИЛИ-НЕ или И-НЕ.

1-я схема – на элементах ИЛИ-НЕ, 2-я – на И-НЕ. Недостаток: неопределенное состояние. Для исключения неопределенного состояния разработаны модификации RS-триггеров, у которых при запрещенных входных комбинациях выходной сигнал принимает следующие значения: R-триггер - 0 S-триггер - 1 E-триггер – Qn JK-триггер -

Триггерные системы Триггерные системы – это RS-триггер как ячейка памяти и устройство управления (УУ).

J, K, V, (T)C – внешние входы; Ra, Sa – внешние входы ячейки памяти; Q, V – разрешающий сигнал (подготавливает вход разрешения приёма информации) RS – информационный сигнал C – синхронизирующий (тактирующий) Ra,Sa – входы асинхронной установки в 0 или 1 состояние T – вход счётного триггера (счётный вход) D – вход установки D или DV-триггера в 0 или 1 состояние

Функциональное назначение внешних входов

УУ – комбинационное устройство, преобразующее входную информацию в комбинацию сигналов под воздействием которых ячейка памяти принимает одно из двух устойчивых состояний. Изменяя схему УУ и способы ее связи с ячейкой памяти можно получить триггеры с различными функциональными свойствами. Сигнал на информационном входе определяется информацией, которая будет записываться с триггер. С помощью подготовительного сигнала можно в нужный момент прервать действие триггера или группы триггеров, сохраняя информацию на выходе (V-сигнал). Исполнительные сигналы (С-сигнал) задают момент приема входной информации и служат для синхронной работы ряда устройств, образующих функциональные узлы. Асинхронные и синхронные триггеры

По способу ввода информации бывают асинхронные и синхронные триггеры. Асинхронные триггеры имеют только информационный вход и срабатывают непосредственно за изменением сигналов на входе. У синхронных триггеров смены информации на информационных входах недостаточно для срабатывания. Необходим дополнительный импульс, подаваемый на тактирующий вход. Синхронные сигналы вырабатывают специальными генераторами тактирующих импульсов, которые задают частоту смены информации. Статическое управление – переключение происходит в момент действия синхронизирующего импульса. Основной недостаток – незащищенность перед опасными состязаниями сигналов, то есть возникновение временных сдвигов из-за различных задержек распространения сигнала, проходящего по различным цепям, низкая помехоустойчивость.

При введении синхронизации увеличивается помехозащищённость. Срабатывание синхронных триггеров происходит при поступлении тактовых импульсов, длительность которых гораздо меньше их периода. В остальное время на входной сигнал триггер не реагирует, то есть, по сравнению с асинхронным, обладает более высокой помехоустойчивостью.

Поиск по сайту: |

.

.

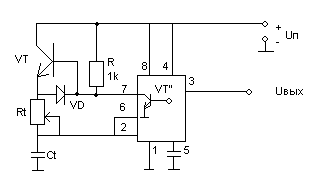

(высокий уровень). VT открыт, и Ct заряжается по цепи: +Uп – VT – Rt – Ct. Как только

(высокий уровень). VT открыт, и Ct заряжается по цепи: +Uп – VT – Rt – Ct. Как только  достигает

достигает  , схема перебрасывается

, схема перебрасывается  , и Ct разряжается по цепи: Ct – Rt – VD – 7. Т.к. и заряд, и разряд происходит через один и тот же резистор, время импульса практически равно времени паузы. Погрешность может вызывать неодинаковое падение напряжения на VT и VD, что актуально при малых значениях Rt.

, и Ct разряжается по цепи: Ct – Rt – VD – 7. Т.к. и заряд, и разряд происходит через один и тот же резистор, время импульса практически равно времени паузы. Погрешность может вызывать неодинаковое падение напряжения на VT и VD, что актуально при малых значениях Rt.

. VT3 и VT4 осуществляют защиту преобразователя от токовых перегрузок и к.з. нагрузки. При превышении

. VT3 и VT4 осуществляют защиту преобразователя от токовых перегрузок и к.з. нагрузки. При превышении  становится равным 0,12*5,1=0,6, VT3 и VT4 отпираются, напряжение на 4-ом выводе DA стремится к нулю и DA прекращает выработку управляющих импульсов.

становится равным 0,12*5,1=0,6, VT3 и VT4 отпираются, напряжение на 4-ом выводе DA стремится к нулю и DA прекращает выработку управляющих импульсов.

- амплитуда ВЧ колебаний;

- амплитуда ВЧ колебаний;  - модулирующее напряжение;

- модулирующее напряжение;  - амплитуда несущей частоты.

- амплитуда несущей частоты.

– амплитуда колебаний в режиме молчания;

– амплитуда колебаний в режиме молчания;

–частота несущей;

–частота несущей;  - частота модуляции;

- частота модуляции;  - индекс модуляции;

- индекс модуляции;  - девиация частоты.

- девиация частоты.

- функция Бесселя 1-го рода n-го порядка от индекса модуляции.

- функция Бесселя 1-го рода n-го порядка от индекса модуляции.

- полоса частот, Гц.

- полоса частот, Гц.

– заряд электрона,

– заряд электрона,  ;

;  - постоянный ток, проходящий через резистор;

- постоянный ток, проходящий через резистор;  - полоса частот, Гц.

- полоса частот, Гц.

Ом выбор определяется конкретными приборами.

Ом выбор определяется конкретными приборами. всегда будет преобладать шум напряжения, и коэффициент шума будет неудовлетворительным. В этом случае лучше использовать трансформатор для увеличения уровня сигнала и сопротивления источника сигналов.

всегда будет преобладать шум напряжения, и коэффициент шума будет неудовлетворительным. В этом случае лучше использовать трансформатор для увеличения уровня сигнала и сопротивления источника сигналов.

эмиттерный переход закрыт, а коллекторный открыт и напряжение на базе VT1=1.8 В. VT2 и VT5 открыты, VD4 –предназначен для надежного запирания VT4. R3, R4 и VT3 действуют как резистор и предназначены для увеличения помехоустойчивости.

эмиттерный переход закрыт, а коллекторный открыт и напряжение на базе VT1=1.8 В. VT2 и VT5 открыты, VD4 –предназначен для надежного запирания VT4. R3, R4 и VT3 действуют как резистор и предназначены для увеличения помехоустойчивости.

, вычитание

, вычитание  )

) , RSP и др.

, RSP и др.