|

|

|

Архитектура Астрономия Аудит Биология Ботаника Бухгалтерский учёт Войное дело Генетика География Геология Дизайн Искусство История Кино Кулинария Культура Литература Математика Медицина Металлургия Мифология Музыка Психология Религия Спорт Строительство Техника Транспорт Туризм Усадьба Физика Фотография Химия Экология Электричество Электроника Энергетика |

Цифровые процессоры на ПЗС-структурах

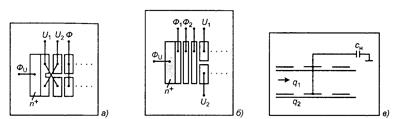

Цифровые ПЗС предназначены для обработки сигналов в виде дискретных функций, и их можно разделить на структуры для арифметико-логической обработки информации и структуры для хранения информации - запоминающие устройства. В цифровые ПЗС можно включить регистры сдвига, логические и арифметические устройства, запоминающие устройства. В них информация представляется двумя уровнями зарядов, локализованных в потенциальной яме под затвором. Состояние логической единицы определяется максимальным зарядовым пакетом в яме, состояние логического нуля - отсутствием заряда или величиной фонового заряда. Следует заметить, что цифровые устройства ПЗС являются устройствами динамического типа, т. к. необходима регенерация информации. К основным аналоговым операциям относятся сложение, вычитание, умножение, умножение на весовой коэффициент, дифференцирование, интегрирование. Операцию аналогового сложения в зарядовой форме можно произвести различными способами, зависящими от конструкции ПЗС. В схемах параллельного сложения зарядовые пакеты величиной Q1, Q2 и Q3, передаются по п-параллельным каналам ПЗС (рис. 4.15, а). Суммирующий элемент должен иметь зарядовую связь с элементами цепочек. Суммирование осуществляется в процессе слияния всех зарядов q, из параллельных цепочек в потенциальную яму суммирующего элемента, т. е.

q1 + q2 + ... + qn = QS < СS(Uф - Uсм), (4.13)

где QS - суммарный заряд, который должен уменьшаться в потенциальной яме суммирующего элемента емкостью СS. В схеме последовательного сложения между суммирующими последними тактовыми электродами расположен экранирующий электрод, создающий потенциальный барьер и препятствующий обратной передаче зарядов из суммирующего элемента (рис. 4.15, б). На суммирующий затвор подается импульс ФS длительность которого больше периода следования тактовых импульсов. На срезе распределения фазы Фз, очередной зарядовый пакет перетекает через экранирующий элемент в потенциальную яму суммирующего элемента и складывается с ранее переданными зарядами. Зарядовая емкость суммирующего элемента определяется условием:

Рис. 4.15. Схемы суммирования зарядовых пакетов: а - параллельный; б - последовательный; в - на плавающих затворах

Аналогичным способом зарядовые пакеты можно суммировать в плавающей диффузионной области. В каждый элемент поступает определенный зарядовый пакет. На общей шине находится емкостная нагрузка. Используя принцип суперпозиции, можно вычислить изменение потенциала при суммировании зарядового пакета на общей шине нагрузочной емкости. Полное изменение потенциала при поступлении зарядовых пакетов во все элементы определяется выражением:

Таким образом, выходной сигнал на плавающей шине будет пропорционален сумме зарядовых пакетов. Этот прием позволяет производить суммирование без разрушения зарядового пакета. Операцию вычитания аналоговых сигналов можно производить различными способами (рис. 4.16). Одним из способов является формирование пакета заряда, пропорционального разности напряжений на электродах (рис. 4.16, а). В этом случае используются перекрестные связи затворов, которые управляются напряжениями аналоговых сигналов U1 и U2. Если U1 > U2, то в верхнюю цепочку элементов заряд не поступает вследствие более глубокой потенциальной ямы в первом элементе верхней цепочки по сравнению со второй.

Рис. 4.16. Схемы вычитания зарядовых пакетов: а - с перекрестными связями; б - с зарядом смещения; в - на плавающих затворах

Таким образом, после этапа экстракции электроны будут экстрагированы обратносмещенной п+-областью истока. В нижнюю цепочку будет введен зарядовый пакет величиной

q2 = SC(U1 - U2), q1 = 0.(4.16)

Для случая U1 < U2заряд вводится только в верхнюю цепочку, т. е.

q1 = SCД(U2 – U1), q2 = 0.(4.17)

Итак, разность двух сигналов (U2 – U1) формируется в нижней цепочке, если разность положительная, и в верхней - при отрицательной разности. При считывании сигналов из обеих цепочек можно определить как разность потенциалов U1 - U2, так и знак этой разности. Другой способ предусматривает представление входных сигналов в виде зарядовых пакетов. Разностный сигнал преобразуется в нужную форму: в виде заряда или напряжения (рис. 4.16, б). Во входной элемент инжекции - экстракции вводится фиксированный зарядовый пакет q0. Этот заряд делится между двумя элементами, затворы которых находятся под напряжением U1 и U2. При достаточно медленном спаде напряжения на шине Ф2 соблюдаются квазистатические условия передачи. Это означает, что поверхностный потенциал шины Ф2 и электродов U1 и U2 одинаковы и j1 = j2. Если

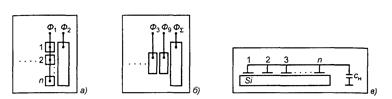

S1= S2 = S, (4.18) q1 = q2 = q, (4.19) то q1 =1/2[q0 + SCД(U1 – U2)],(4.20) q2 =1/2[q0 + SCД(U2 – U1)].(4.21) Таким образом, в верхней и нижней цепочке электродов будут передаваться заряды, отличающиеся от половинного заряда q0/2 на величину, пропорциональную разности входных сигналов (U1 - U2). При считывании выходной сигнал будет смещен относительно среднего уровня, соответствующего q0/2 (при U1 = U2), на величину, пропорциональную (U2 – U1). Операцию вычитания можно реализовать на плавающих затворах (рис. 4.16, в). При этом используется эффект умножения потенциала затвора при передаче зарядового пакета в элемент с плавающим затвором. Если объединить два плавающих затвора и в один вводить заряд q1, а из другого выводить заряд q2, то заряд q1 вызовет понижение потенциала, а выводимый заряд q2 - повышение потенциала плавающего затвора. Результирующее изменение потенциала плавающей шины будет пропорционально разности зарядовых пакетов, передающихся по верхним и нижним цепочкам. Операцию дифференцирования можно реализовать путем соединения плавающих затворов двух соседних разрядов (рис. 4.17, а). При этом зарядовый пакет Qn(nT) из элементов1 экстрагируется и вызывает увеличение потенциала UA, одновременно в элемент2вводится зарядовый пакет Qn[(n + 1)T], соответствующий следующей выборке сигнала. На плавающей шине формируется сигнал, пропорциональный разности двух зарядов или производной передаваемого аналогового сигнала. Операция интегрирования сигнала является обратной операции дифференцирования и осуществляется суммированием (накоплением) зарядовых пакетов. На ПЗС-структурах выполняют аналогово-цифровые и цифроаналоговые процессоры, мультиплексоры и демультиплексоры. Мультиплексор, например, служит для временной задержки и накопления информации (рис. 4.17, б). Тактовая частота подбирается таким образом, чтобы задержка между отдельными входами была равна времени перемещения изображения между входными приемниками. При этом происходит когерентное сложение зарядовых пакетов. Важно отметить, что шумы складываются некогерентно. Логические ячейки и операции могут быть реализованы с помощью комбинации уже рассмотренных устройств, предназначенных для арифметических операций.

Рис. 4.17. Схемы дифференцирования и умножения сигналов (а) и мультиплексора (б)

Подадим на входные электроды в отдельности или на оба сразу напряжение, соответствующее логической единице. Возникающий зарядовый пакет также будет иметь величину, соответствующую логической единице (рис. 4.18). С любого из входовX1 илиХ2 зарядовый пакет, благодаря зарядовой связи перемещается под общий электрод и далее индицируется как логическая единица. Если же логическая единица подается сразу на оба входа, то на общем электроде будет удвоенный заряд. Для преобразования такого удвоенного зарядового пакета в зарядовый пакет, соответствующий логической единице, формируется регулируемый сток заряда. Он отделяется от потенциальной ямы под общим электродом с помощью потенциального барьера в виде ионно-легированной области. Высота барьера выбирается такой, чтобы в потенциальной яме оставался зарядовый пакет, строго соответствующий логической единице. Стоком является обратносмещенный р-п-переход. На рис. 4.18, а представлена логическая ПЗС-ячейка, выполняющая операцию логического сложения (ИЛИ). Логическая ячейка для операции логического умножения (И) строится аналогично ячейке типа ИЛИ. За время действия напряжения фазы Ф1 потенциальные ямы образуются под электродами D и С. Под электрод С заряд попадает только в том случае, если на оба входа X1 иХ2 подаются одновременно зарядовые пакеты, соответствующие логической единице. По окончании действия фазового напряжения Ф1 начинает действовать напряжение Ф2. Этим напряжением зарядовый пакет перемещается на выход из-под электрода С, а из-под электрода D переводится в обратносмещенную область и затем экстрагируется. По такому принципу конструируются логические ячейки, выполняющие комбинацию логических функций. Малые размеры логических ячеек позволяют формировать сложные арифметико-логические устройства.

Рис. 4.18. Логические ПЗС-ячейки: а - схема реализации функции ИЛИ; б - функции И

Поиск по сайту: |

(4.14)

(4.14)

.(4.15)

.(4.15)