|

|

|

Архитектура Астрономия Аудит Биология Ботаника Бухгалтерский учёт Войное дело Генетика География Геология Дизайн Искусство История Кино Кулинария Культура Литература Математика Медицина Металлургия Мифология Музыка Психология Религия Спорт Строительство Техника Транспорт Туризм Усадьба Физика Фотография Химия Экология Электричество Электроника Энергетика |

Определение среднего времени распространения логического сигнала

1.10.1 Определение среднего времени задержки распространения сигнала D осуществите, собрав схему рисунка 1.11. Для этого выберите микросхему, содержащую не мене 3х логических элементов.

Рисунок 1.11 - Схема измерения среднего времени задержки распространения сигнала

Устройство на 3х логических элементах с обратной связью будет генерировать непрерывную последовательность логических сигналов с периодом Т и скажностью, равной 2, за счет фазового сдвига выходного сигнала схемы относительно входного, обусловленного временем задержки распространения сигнала и трехкратным переворотом фазы сигнала инверторами. Среднее время задержки распространения сигнала D одного элемента схемы рассчитывается по формуле:

где: T- период генерируемых сигналов; t01 - среднее время задержки одного логического элемента при переходе из состояния 0 в состояние 1; t10 - среднее время задержки одного логического элемента при переходе из состояния 1 в состояние 0. Примечание - Если полоса пропускания усилителя Y осциллографа меньше 50 мГц, то на экране осциллографа будет наблюдаться периодический сигнал, близкий по форме к гармоническому сигналу.

Содержание отчета

Отчет должен быть выполнен в соответствии с СТП 101-00 и содержать: - описание принципиальных схем, принципа действия испытанных логических элементов в объеме, достаточном для успешной защиты выполненного практикума; - схемы экспериментов, составленные в процессе подготовки и проведения работы; - результаты исследования логических элементов, которые тестировались на стенде; - выводы к практикуму.

Условно-графические и буквенно-цифровые обозначения логических элементов

Рисунок 1.13 – Условно-графические и буквенно-цифровые обозначения логических микросхем 2 Практикум "Комбинационные логические схемы"

Практикум предназначен для изучения принципов построения и работы комбинационных логических схем, выполненных по КМОП и TTL технологиям, изучение практических методов их анализа. В этот раздел практикума включены методики проверки в статическом режиме алгоритмов функционирования дешифраторов, мультиплексоров и сумматоров. Дешифраторы

Дешифраторы относятся к комбинационным схемам, которые предназначены для преобразования двоичного или двоично-десятичного кода в позиционный. Условное обозначение двоичного дешифратора показано на рисунке 2.1.

Рисунок 2.1 – Условно-графическое обозначение двоичного дешифратора

Данный дешифратор имеет четыре входа и 16 выходов. В зависимости от разрядности дешифрируемого кода и функциональных возможностей интегральных схем (ИС), имеющихся в распоряжении разработчика, дешифратор может быть выполнен на основе одноступенчатой (линейной) или многоступенчатой схем дешифрации. Линейные дешифраторы выполняются без какого-либо их логического преобразования прямой схемной реализацией выражения вида:

:

где: n=2m – число выходов; m – число разрядов входного кода.

Таким образом, линейный дешифратор представляет собой 2m независимых по выходам вентилей с m входами каждый. На рисунке 2.2 показана схема четырехвходового линейного дешифратора.

Рисунок 2.2 – Функциональная схема 4х входового линейного дешифратора

Одноступенчатые дешифраторы эффективны, когда разрядность входного кода не превышает числа входов схемы И типового логического элемента ИС. Быстродействие линейного дешифратора наибольшее среди других типов дешифраторов и равно среднему времени задержки одного элемента tср. Одной из первых ИС линейных дешифраторов является схема SN7445 фирмы TEXAS (USA), показанная на рисунке 2.3.

Рисунок 2.3 – Функциональная схема линейного двоично-десятичного дешифратора SN7445

SN7445 - двоично-десятичный дешифратор, преобразующий двоично-десятичный код в позиционный десятиразрядный код. На рисунке 2.4 показана структурная схема построения прямоугольного дешифратора на 256 выходов. Прямоугольный или матричный дешифратор содержит первую ступень из нескольких линейных дешифраторов (ЛД), на каждом из которых дешифрируется группа разрядов входного слова. Количество (ЛД) определяется числом групп, на которое разбивается входное слово. Во второй ступени прямоугольного дешифратора осуществляется совпадение каждого с каждым выходных сигналов первых двух ЛД по матричной схеме на двухвходовых вентилях. В третьей ступени производится операция "И" выходных сигналов 2ой ступени с незадействованными выходами 1ой ступени также по матричной схеме на двухвходовых вентилях.

Рисунок 2.4 – Структурная схема прямоугольного матричного дешифратора При оптимальном разбиении входного слова общее число двухвходовых вентилей, необходимых для построения двухступенчатого матричного дешифратора равно:

Nч = 2m+2(m/2)+1 – при четном (m+1),

Nн=2m+2(m-1)/2+2(m+1)/2 – при нечетном (m+1).

Быстродействие матричных дешифраторов составляет величину равную не менее k×tср., где k×- число ступеней дешифратора (k=m-1). Другой разновидностью многоступенчатых дешифраторов являются пирамидальные дешифраторы. Особенностью пирамидального дешифратора является применение во всех ступенях дешифрации двухвходовых вентилей с обязательным подключением выхода элемента i-й ступени ко входам только двух элементов (i+1)-й ступени. Число ступеней k - пирамидального шифратора на единицу меньше разрядности дешифрируемого числа. Число вентилей в каждой ступени определяется из выражения: 2 i+1, где i - номер ступени. Общее количество вентилей на дешифратор равно:

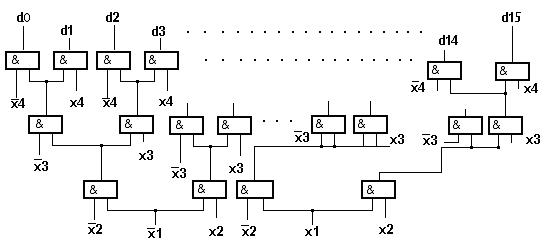

На рисунке 2.5 показан пирамидальный дешифратор на 16 выходов.

Рисунок 2.5 – Структурная схема пирамидального дешифратора

Пирамидальные дешифраторы значительно уступают по быстродействию линейным дешифраторам, т.к. время задержки равно:

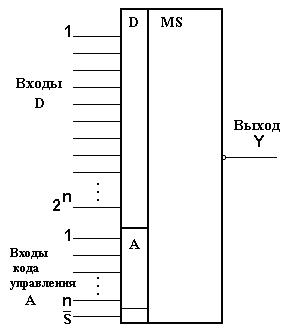

tз = tср.(m-1). Мультиплексоры Мультиплексоры - это комбинационные устройства, предназначенные для коммутации одного из нескольких источников логических сигналов к одной выходной шине. Обозначение мультиплексора приведено на рисунке 2.6.

Рисунок 2.6 – Условно - графическое обозначение мультиплексора

Мультиплексор имеет 2n входов для данных D, n управляющих (адресных) входов А (может также иметь входную логику для выбора кристалла), один выход Ym (вход стробирующего сигнала В последнем случае большой интерес представляют КМОП-мультиплексоры, в которых роль коммутаторов выполняют двухнаправленные КМОП- ключи, как показано на рисунке 2.8. Такие ключи осуществляют двухстороннюю передачу не только логического сигнала, но и аналогового. Таким образом, КМОП - мультиплексор является одновременно и двухсторонним коммутатором аналоговых сигналов. Мультиплексоры, имеющие режим высокого выходного сопротивления (в частности КМОП - мультиплексоры) могут объединяться по выходам для подключения к общей шине без дополнительных согласующих элементов. Временные характеристики мультиплексоров задаются по трем трактам: вход адреса – выход, вход данных – выход, вход стробирующего сигнала – выход. Для большинства мультиплексоров быстродействие определяется задержкой равной t = (1-2)tср..

Рисунок 2.7 – Функциональная схема мультиплексора К155КП1

Рисунок 2.8 – Структурная схема мультиплексора с ключами на КМОП транзисторах

Сумматоры Сумматоры предназначены для выполнения арифметических и логических операций над числами, представленными в двоичном, двоично-десятичном и других кодах. Различают одноразрядные и многоразрядные, последовательные и параллельные сумматоры. В цифровых схемах применяются одноразрядные сумматоры на два (полусумматор) и на три входа (полный одноразрядный сумматор). Логические функции, реализуемые полусумматором:

S=A+B,

P=AB , где: S - сумма; A, B - входы слагаемых; P - выход разряда переноса.

Логические функции, реализуемые полным сумматором:

S=A+B+C,

P=AB+AC+BC,

где: С - вход переноса для подключения сигнала переноса с сумматора предыдущего разряда. Полные сумматоры можно объединять в параллельные многоразрядные сумматоры. На рисунке 2.9 приведена схема двухразрядного сумматора ИС типа SN7482.

Рисунок 2.9 – Функциональная схема двухразрядного сумматора типа SN7482 Положительным свойством такой реализации является отсутствие инверсных входов, что позволяет на небольшом числе выводов ИС увеличить ее функциональную сложность. Задержка формирования суммы при этом равна 2tср, где tср – среднее время задержки одного логического элемента. На рисунке 2.10 приведено обозначение полного четырехразрядного сумматора - ИС типа К155ИМ3.

Рисунок 2.10 – Условно - графическое обозначение четырехразрядного сумматора К155ИМЗ

2.4 Контрольные вопросы

1 Дайте классификацию комбинационных схем. 2 Объясните отличительные особенности функционирования различных комбинационных схем. 3 Перечислите и опишите принципы построения дешифраторов, как на функциональном, так и на уровне логических элементов. 4 От чего зависят сложность и быстродействие дешифратора? 5 Перечислите и опишите принципы построения мультиплексоров на функциональном уровне. 6 От чего зависят функциональные возможности мультиплексоров? 7 Как производится подготовка стенда для выполнения практикума? 8 Каков порядок выполнения практикума? 9 Объясните принцип работы сумматора. 10 Как осуществляется синтез и анализ комбинационных схем? 11 Поясните, что такое состязания, как их можно выявить и устранить. 12 Объясните работу всех приведенных в описании практикума схем, их особенности. 13 Что представляет собой сумматор с ускоренным переносом?

Поиск по сайту: |

,

,

,

, ,

, ,

, ,

,

). Логическая схема мультиплексора показана на рисунке 2.7 и включает в себя дешифратор и коммутаторы сигналов, объединенные по выходам. Причем, объединение по выходам может осуществляться двумя способами: объединение с помощью многовходового логического элемента ИЛИ либо с помощью монтажного ИЛИ.

). Логическая схема мультиплексора показана на рисунке 2.7 и включает в себя дешифратор и коммутаторы сигналов, объединенные по выходам. Причем, объединение по выходам может осуществляться двумя способами: объединение с помощью многовходового логического элемента ИЛИ либо с помощью монтажного ИЛИ.