|

|

|

Архитектура Астрономия Аудит Биология Ботаника Бухгалтерский учёт Войное дело Генетика География Геология Дизайн Искусство История Кино Кулинария Культура Литература Математика Медицина Металлургия Мифология Музыка Психология Религия Спорт Строительство Техника Транспорт Туризм Усадьба Физика Фотография Химия Экология Электричество Электроника Энергетика |

Программная модель IA-32 ⇐ ПредыдущаяСтр 6 из 6

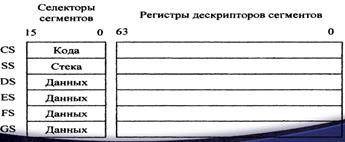

Любая выполняющаяся программа получает в свое распоряжение определенный набор ресурсов процессора. Эти ресурсы необходимы для обработки и хранения в памяти команд и данных программы, а также информации о текущем состоянии программы и процессора. Программную модель процессора в архитектуре IA-32 процессоров Intel составляет следующий набор ресурсов: пространство адресуемой памяти до 232 - 1 байт (4 Гбайт), для Pentium III/IV -до 236 - 1 байт (64 Гбайт); набор регистров для хранения данных общего назначения; набор сегментных регистров; набор регистров состояния и управления; набор регистров устройства вычислений с плавающей точкой (сопроцессора); набор регистров целочисленного MMX-расширения, отображенных на регистры сопроцессора (впервые появились в архитектуре процессора Pentium MMX); набор регистров MMX-расширения с плавающей точкой (впервые появились в архитектуре процессора Pentium III); программный стек - специальная информационная структура, работа с которой предусмотрена на уровне машинных команд (более подробно она будет обсуждена позже). Это основной набор ресурсов. Кроме того, к ресурсам, поддерживаемым архитектурой IA-32, необходимо отнести порты ввода-вывода, счетчики мониторинга производительности. Программные модели более ранних процессоров (i486, первые Pentium) отличаются меньшим размером адресуемого пространства оперативной памяти (232 - 1, так как разрядность их шины адреса составляет 32 бита) и отсутствием некоторых групп регистров. Сегментные регистры Процессоры Intel аппаратно поддерживают сегментную организацию программы. Это означает, что любая программа состоит из трех сегментов: кода, данных и стека. Логически машинные команды в архитектуре IA-32 построены так, что при выборке каждой команды для доступа к данным программы или к стеку неявно используется информация из вполне определенных сегментных регистров. В зависимости от режима работы процессора по их содержимому определяются адреса памяти, с которых начинаются соответствующие сегменты. В программной модели IA-32 имеется шесть сегментных регистров CS, SS, DS, ES, GS, FS, служащих для доступа к четырем типам сегментов. Сегмент кода содержит команды программы. Для доступа к этому сегменту служит регистр сегмента кода (Code Segment register) CS. Он содержит адрес сегмента с машинными командами, к которому имеет доступ процессор (эти команды загружаются в конвейер процессора). Сегмент данных содержит обрабатываемые программой данные. Для доступа к этому сегменту служит регистр сегмента данных (Data Segment register) DS, который хранит адрес сегмента данных текущей программы. Сегмент стека представляет собой область памяти, называемую стеком. Работу со стеком процессор организует по следующему принципу: последний записанный в эту область элемент выбирается первым. Для доступа к этой области служат регистр сегмента стека (Stack Segment register) SS, содержащий адрес сегмента стека. № Дополнительный сегмент данных. Неявно алгоритмы выполнения большинства машинных команд предполагают, что обрабатываемые ими данные расположе -ны в сегменте данных, адрес которого находится в регистре сегмента данных DS. Если программе недостаточно одного сегмента данных, то она имеет возможность задействовать еще три дополнительных сегмента данных. Но в отличие от основного сегмента данных, адрес которого содержится в регистре DS, при использовании дополнительных сегментов данных их адреса требуется указывать явно с помощью специальных префиксов переопределения сегментов в команде. Адреса дополнительных сегментов данных должны содержаться в регистрах дополнительного сегмента данных (Extension Data Segment registers) ES, GS, FS. Системные регистры процессора Использование их жестко регламентировано. Именно они обеспечивают работу защищенного режима. Их также можно рассматривать как часть архитектуры процессора, которая намеренно оставлена видимой. Системные регистры можно разделить на три группы: -четыре регистра управления; -четыре регистра системных адресов; -восемь регистров отладки. В состав системных регистров процессоров ряда Pentium введены следующие изменения: задействован ранее зарезервированный регистр управления CR4; добавлена группа MSR-РЕГИСТРОВ (MSR — MODEL SPECIFIC REGISTER, модельно-зависимые регистры процессора), назначение и возможности которых подчиняются архитектуре конкретной модели процессора. Ранее их функции частично выполняли тестовые регистры, вошедшие теперь в состав MSR-группы. Для доступа к этим регистрам предусмотрены специальные команды.

Поиск по сайту: |