|

|

|

Архитектура Астрономия Аудит Биология Ботаника Бухгалтерский учёт Войное дело Генетика География Геология Дизайн Искусство История Кино Кулинария Культура Литература Математика Медицина Металлургия Мифология Музыка Психология Религия Спорт Строительство Техника Транспорт Туризм Усадьба Физика Фотография Химия Экология Электричество Электроника Энергетика |

Ієрархічна структура пам’яті ПК (намалюйте схему й поясніть її). Намалюйте схему регістра та опишіть його роботу за допомогою діаграми

Регистр — последовательное или параллельное логическое устройство, используемое для хранения n-разрядных двоичных чисел и выполнения преобразований над ними. Регистр представляет собой упорядоченную последовательность триггеров, обычно D, число которых соответствует числу разрядов в слове. С каждым регистром обычно связано комбинационное цифровое устройство, с помощью которого обеспечивается выполнение некоторых операций над словами. Фактически любое цифровое устройство можно представить в виде совокупности регистров, соединённых друг с другом при помощи комбинационных цифровых устройств. Основой построения регистров являются D-триггеры, RS-триггеры. Операции в регистрах Типичными являются следующие операции: · приём слова в регистр; · передача слова из регистра; · поразрядные логические операции; · сдвиг слова влево или вправо на заданное число разрядов; · преобразование последовательного кода слова в параллельный и обратно; · установка регистра в начальное состояние (сброс). Регистры классифицируются по следующим видам: · накопительные (регистры памяти, хранения); · сдвигающие]. В свою очередь сдвигающие регистры делятся: · по способу ввода-вывода информации: · параллельные - запись и считывание информации происходит одновременно на все входы и со всех выходов[15]; · последовательные - запись и считывание информации происходит в первый триггер, а та информация, которая была в этом триггере, перезаписывается в следующий - то же самое происходит и с остальными триггерами[16][17]; · комбинированные; · по направлению передачи информации: · однонаправленные; · реверсивные[18][19]. · по основанию системы счисления · двоичные · троичные · десятичные

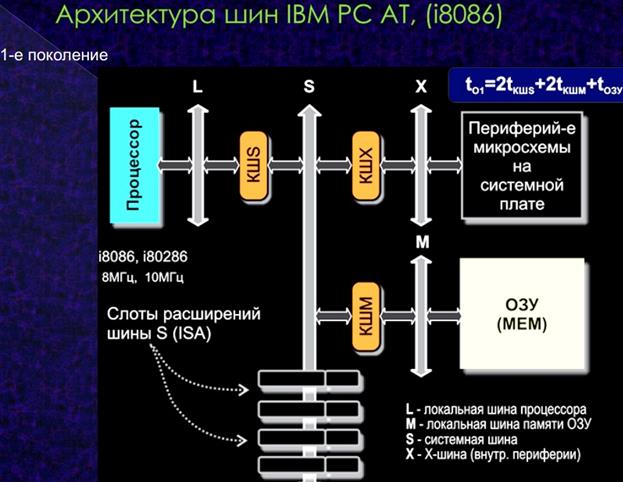

Багаторівнева архітектура шин персонального комп’ютера: локальні шини, системна шина, шина внутрішньої периферії (блок-схема, властивості й призначення шин). Опишіть основні етапи еволюції шин ПК.

Опишіть функції, які виконують північний та південний мости (чипсети, контролери шин) материнської плати комп’ютера. Які пристрої підключаються до мостів ПК? Які пристрої може містити найпростіший контролер шини? Намалюйте схему логічного дешифратора з чотирма входами. Чипсет ( Chipset ) – основа системной платы, - это набор микросхем системной логики. Посредством чипсета происходит взаимодействие всех подсистем ПК. Чипсеты обладают высокой степенью интеграции, и представляют собой две микросхемы, в которых реализованы интегрированные контроллеры, обеспечивающие работу и взаимодействие основных подсистем компьютера. Практически у всех современных чипсетов, набор системной логики состоит двух микросхем северного и южного мостов. Название микросхем обусловлено их положением относительно шины PSI: северный - выше, южный - ниже. Микросхема северного моста обеспечивает работу с наиболее скоростными подсистемами. Он содержит: контроллер системной шины, посредством которого происходит взаимодействие с процессором; контроллер памяти, осуществляющий работу с системной памятью контроллер графической шины AGP (AcceleratedGraphicsPort), обеспечивающий взаимодействие с графической подсистемой (сегодня большинство чипсетов поддерживают интерфейсы 1х/2х/4х, скоро в перспективе 8-я скорость AGP); контроллер шины связи с южным мостом (PCI – шины в классическомпонимании). Задача северного моста - с минимальными задержками организовать обслуживание запросов к системной памяти. Решения этой задачи основаны на реализации контроллера памяти, позволяющего одновременно обрабатывать большое количество запросов и данных, расставляя приоритеты и очерёдность доступа к основной памяти. Южный мост обеспечивает работу с более медленными компонентами системы и периферийными устройствами. Для южного моста стало стандартом наличие следующих контроллеров и устройств: 1. Двухканальный (PrimarySecondary) IDE-контроллер, обеспечивающий работу с внутренними (то есть расположенными внутри корпуса ПК) накопителями, в частности с винчестерами и оптическими дисководами (CD-ROM, DVD-ROM, CD-R/RW и т.д.), оснащенными соответствующим интерфейсом. 2. USB-контроллер (один и более), обеспечивающий работу с устройствами, подключаемыми к универсальной последовательной шине (USB), USB должен заменить устаревшие внешние интерфейсы, такие как последовательный RS-232 (COM-порт) и параллельный IEEE-1284 (LPT-порт). 3. Контроллер шины LPC (LowPinCountInterface), который пришел на смену устаревшей ISA. Шина LPC имеет 4-битный интерфейс, соединённый с чипом ввода-вывода (Super I/O chip), который поддерживает работу внешних портов (последовательный COM и параллельный LPT, PS/2 и инфракрасного), а так же контроллер флоппи-дисковода. Контроллер — это электронное устройство, предназначенное для подключения к магистрали компьютера разных по принципу действия, интерфейсу и конструктивному исполнению периферийных устройствК термину "контроллер" очень близок по смыслу другой термин —"адаптер". Назначение обоих одинаково, но контроллер несколько сложнее: "подразумевается его некоторая активность — способность к самостоятельным действиям после получения команд от обслуживающей его программы. Сложный контроллер может иметь в своем составе и собственный процессор"". На уровне рядового пользователя данные понятия практически неразличимы и могут считаться синонимами. Дешифратор типа ИД3 - полный, имеет четыре адресных входа# 1,2,4,8, два входа стробирования Е1,Е2 и шестнадцать выходов 0-15. Если на обоих входах стробирования уровни логического 0, то на том из выходов, номер которого соответствует значению двоичного входного кода, будет уровень логического 0, на остальных выходах - логической 1. Если хотя бы на одном из входов стробирования уровень логической 1, то независимо от состояний входов на всех выходах ИС формируется 1. Увеличить разрядность дешифратора можно, используя входы стробирования. Так, на рис.94б приведена схема пятиразрядного дешифратора. Старший разряд используется в этом случае для выбора ИС дешифратора.

Опишіть структуру шин комп’ютера в «динамікові часу», на якій показано основні компоненти, що збільшують продуктивність ПК (приведіть блок-схему і еволюцію назв шин та процесорів). Окремо намалюйте таблицю з характеристик шин ПК (ISA, PCI, PCI-express). 1)X-Bus, LPC. (8086) 2) ISA,PCI. 3)ISA, EISA, PCI, PCI Express. (i386) 4) VL-Bus, AGP, PCI-Express 16x

Шина ISA была первой стандартизированной системной шиной (ISA означает IndustryStandartArchitecture) и долгие годы являлась стандартом в области РС. И даже сегодня разъемы этой шины можно встретить на некотороых системных платах. Родоначальником в семействе шин ISA была появившаяся в 1981 году 8-разрядная шина (8 bit ISA Bus), которую можно встретить в компьютерах ХТ-генерации. 8-разрядная шина имеет 62 линии, контакты которых можно найти на ее слотах. Они включают 8 линий данных, 20 линий адреса, 6 линий запроса прерываний. Шина функционирует на частоте 4.77 MHz. 8-разрядная шина ISA - самая медленная из всех системных шин (пропускная способность составляет всего 1.2 Mb в секунду), поэтому она уже давным давно устарела и поэтому сегодня нигде не используется, ну разве что о-о-очень редко (например, некоторые карточки FM-тюнера могут 8-разрядный ISA-интерфейс, так как там шина используется только для управления, а не для передачи собственно данных, и скорость ее работы является некритичной). Дальнейшим развитием ISA стала 16-разрядная шина, также иногда называемая AT-Bus, которая впервые начала использоваться в 1984 году. Если вы посмотрите на ее слоты (извините, пожалуйста, за плохое качество рисунка), то увидите, что они состоят из двух частей, из которых одна (большая) полностью копирует 8-разрядный слот. Дополнительная же часть содержит 36 контактов (дополнительные 8 линий данных, 4 линии адреса и 5 линий IRQ плюс контакт для нового сигнала SBHE). На этом основании короткие 8-разрядные платы можно устанавливать в разъемы новой шины (сделать это наоборот, конечно же, невозможно). PCI (англ. Peripheralcomponentinterconnect, дословно — взаимосвязь периферийных компонентов) — шина ввода/вывода для подключения периферийных устройств к материнской платекомпьютера. Первоначально 32 проводника адрес/данные на частоте 33 МГц. Позже появились версии с 64 проводниками (используется дополнительная колодка разъема) и частотой 66 МГц.Шина децентрализована, нет главного устройства, любое устройство может стать инициатором транзакции. Для выбора инициатора используется арбитраж с отдельно стоящей логикой арбитра. Арбитраж «скрытый», не отбирает времени — выбор нового инициатора происходит во время транзакции, исполняемой предыдущим инициатором.Транзакция состоит из 1 или 2 циклов адреса (2 цикла адреса используются для передачи 64-битных адресов, поддерживаются не всеми устройствами, дают поддержку DMA на памяти более 4 Гб) и одного или многих циклов данных. Транзакция со многими циклами данных называется «пакетной» (burst), понимается как чтение/запись подряд идущих адресов и даёт более высокую скорость — один цикл адреса на несколько, а не на каждый цикл данных, и отсутствие простоев (на «успокоение» проводников) между транзакциями. Спецификация шины PCI

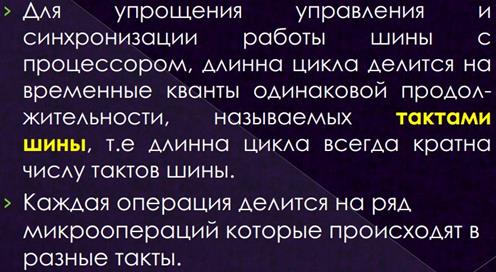

Шина является синхронной - фиксация всех сигналов выполняется по положительному перепаду (фронту) сигнала CLK.Шина PCI все транзакции трактует как пакетные: каждая транзакция начинается фазой (циклом) адреса, за которой может следовать одна или несколько фаз данных. Для адреса и данных используются общие мультиплексированные линии AD. В начале транзакции инициатор активизирует сигнал FRAMES, по шине AD передает целевой адрес, а по линиям C/BE# информацию о типе транзакции (команде). Адресованное целевое устройство отзывается сигналом DEVSEL#, после чего инициатор может указать на свою готовность к обмену данными сигналом IRDY#. Когда к обмену данными будет готово и целевое устройство, оно установит сигнал TRDY#. Данные по шине AD могут передаваться только при одновременном наличии сигналов IRDY# и TRDY#. С помощью этих сигналов инициатор и целевое устройство согласуют свои скорости, вводя такты ожидания. Опишіть загальні принципи організації та роботи шин. Що таке діаграма роботи шини, які умовні позначення присутні на діаграмі і що вони відображають? Що таке цикл, такт (види)? Які дії виконуються протягом першого й наступних тактів шини. Намалюйте приклад роботи шини у вигляді послідовності тактів шини залежних від часу.

Намалюйте діаграму та поясніть принципи роботи асинхронної паралельної шини. Яким чином здійснюється синхронізація в даному типі обміну? Що означає термін квітування? Приведіть приклад паралельної шини персонального комп’ютера схожої архітектури.

Асинхронная шина МС ( разработана в 1974 г. фирмой Computer Automation Inc. ЭВМ) состоит из адресной шины, шин данных, контроля пересылок, арбитража и ряда вспомогательных линий. Вместо перемычек и переключателей МС содержит специальные регистры POS ( Programmable Option Select), позволяющие конфигурировать систему при включении питания. [1] Преимуществаасинхронной шины очевидны, но в действительности большинство шин являются синхронными. [2] Альтернативным методом является применениеасинхронной шины, по которой передача информации в ЦП происходит примерно следующим образом: центральный процессор подает на шину адрес устройства и потенциальный ( а не импульсный) сигнал на специальную линию ( будем называть ее ВВОД), который означает, что данные вводятся в ЦП. После того как ЦП получит этот сигнал, он считает данные с шины и снимет сигнал ВВОД. Когда интерфейс обнаружит, что на линии ВВОД действует НИЗКИЙ уровень, он очистит линии ДАННЫХ и линию ДАННЫЕ ГОТОВЫ. [3] По этой причине были разработаныасинхронные шины, то есть шины без задающего генератора, как показано на рис. 3.35. Здесь ничего не привязывается к генератору. [4] В качестве примера того, как работаетасинхронная шина, рассмотрим временную диаграмму на рис. 3.34. В этом примере мы будем использовать задающий генератор на 40 МГц, который дает цикл шины в 25 не. Хотя может показаться, что шина работает медленно по сравнению с процессорами на 500 МГц и выше, не многие современные шины работают быстрее. Например, шина ISA ( она встроена во все персональные компьютеры с процессором Intel) работает с частотой 8 33 МГц, и даже популярная шина PCI - с частотой 33 МГц или 66 МГц. Причины такой низкой скорости современных шин были даны выше: такие технические проблемы, как перекос шины и требование совместимости. [5] Основными преимуществами шины Futurebus является то, что она представляетсобой высокопроизводительную асинхронную шину независимо от типа процессора и технологии. Шина Futurebus обладает более высокой пропускной способностью, чем другие 32-разрядные шины, благодаря применению более быстродействующих приемо-передатчиков, чем в шинах с ТТЛ-схемотехникой. [6] Наиболее известным является интерфейс ввода-вывода Multibus, фирмы Intel ( табл. 3.6, рис. 3.4), представляющийтактируемую асинхронную шину. [7] Предполагается, что помехоустойчивость синхронных шин выше, чем асинхронных, так как для инициирования синхронной пересылки служит один сигнал тактирования, а в процессе работыасинхронной шины выбросы могут быть восприняты несколькими линиями. Кроме того, линия сигнала тактирования экранируется за счет окружения ее развязанными линиями питания, отводящими выбросы помех на землю. [8] В ЭВМ, которые используют для адресации к оперативной памяти ту же шину, что и для связи с внешними устройствами, применение асинхронного способа дает дополнительное преимущество, так как позволяет применять ЗУ, работающие с различными скоростями. Асинхронные шины используются в некоторых мини - ЭВМ, например в PDP-11, в то время как в микро - ЭВМ и в большинстве мини - ЭВМ применяются синхронные шины. Иногда в синхронных шинах имеется линия готовности, подавая на которую НИЗКИЙ уровень можно приостанавливать дальнейшую активность шины для того, чтобы завершить медленную операцию. [9] Системное управление осуществляется с помощью сигнальных линий BERR, RESET и HALT. Типичными случаями, в которых - используется этот сигнал, являются зависаниеасинхронной шины, например при потере связи, незаконный доступ к памяти при внешнем управлении памятью, а также работа с устройством, которое не реагирует на сигналы во время последовательности обработки векторного прерывания. [10]

Поиск по сайту: |