|

|

|

Архитектура Астрономия Аудит Биология Ботаника Бухгалтерский учёт Войное дело Генетика География Геология Дизайн Искусство История Кино Кулинария Культура Литература Математика Медицина Металлургия Мифология Музыка Психология Религия Спорт Строительство Техника Транспорт Туризм Усадьба Физика Фотография Химия Экология Электричество Электроника Энергетика |

Короткий опис ядра центрального процесорного пристрою AVR ⇐ ПредыдущаяСтр 4 из 4

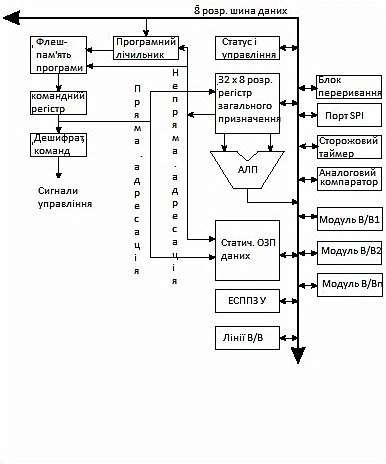

Введення У даному розділі описуються загальні особливості архітектури ядра AVR. Основна функція ядра ЦПУ полягає в гарантуванні коректності виконання програми. Крім цього, ЦПУ повинен мати можливість адресуватися до різних видів пам'яті, виконувати обчислення, управляти периферійними пристроями та обробляти переривання. На рисунку 2.1 зображено короткий огляд архітектури ядра AVR.

Рисунок1.2 - Короткий огляд архітектури ядраAVR З метою досягнення максимальної продуктивності і паралелізму у AVR-мікроконтролерів використовується гарвардська архітектура з роздільними пам'яттю і шинами програм і даних. Команди в пам'яті програм виконуються з однорівневою конвеєризацією. У процесі виконання однієї інструкції наступна попередньо зчитується з пам'яті програм. Дана концепція дозволяє виконувати одну інструкцію за один машинний цикл. Пам'ять програм являє собою внутрішньо-системну програмовану флеш-пам'ять. Регістровий файл з швидким доступом містить 32 x 8-розр. робочих регістрів загального призначення з однотактовим циклом доступу. Завдяки цьому досягнута однотактна робота арифметико-логічного пристрою (АЛП). При звичайній роботі АЛП спочатку з реєстрового файлу завантажується два операнда, потім виконується операція, а після результат відправляється назад в регістровий файл і все це відбувається за один машинний цикл. 6 регістрів з 32 можуть використовуватися як три 16-розр. регістра непрямої адреси для ефективної адресації в межах пам'яті даних. Один з цих покажчиків адреси може також використовуватися як покажчик адреси для доступу до таблиці перетворення у флеш-пам'яті програм. Дані 16-розр. регістри називаються X-регістр, Y-регістр і Z-регістр і описуються далі в цьому розділі. АЛП підтримує арифметичні і логічні операції між регістрами, а також між константою і регістром. Крім того, АЛП підтримує дії з одним регістром. Після виконання арифметичної операції регістр статусу оновлюється для відображення результату виконання операції. Для розгалуження програми підтримуються інструкції умовних і безумовних переходів і викликів процедур, що дозволяють безпосередньо адресуватися в межах адресного простору. Більшість інструкцій являють собою одне 16-розр. слово. Кожна адреса пам'яті програм містить 16- або 32-розр. інструкцію. Флеш-пам'ять програм розділена на дві секції: секція програми початкового завантаження і секція прикладної програми. Обидві секції мають роздільні біти захисту від запису і читання / запису. Інструкція SPM (запис в секцію прикладної програми) повинна використовуватися тільки усередині секції програми початкового завантаження. При генерації переривання і виклику підпрограм адреса повернення з програмного лічильника записується в стек. Стек ефективно розподілений у статичному ОЗП пам'яті даних і, отже, розмір стека обмежений загальним розміром статичного ОЗП і використовуваним його обсягом. У будь-якій програмі відразу після скидання повинна бути виконана ініціалізація покажчика стека (SP) (тобто перед виконанням процедур обробки переривань або викликом підпрограм). Покажчик стека - SP - доступний на читання і запис в просторі вводу-виводу. Доступ до статичного ОЗП даних може бути легко здійснений через 5 різних режимів адресації архітектури AVR. Гнучкий модуль переривань містить свої керуючі регістри в просторі вводу-виводу і має додатковий біт загального дозволу роботи системи переривань в регістрі статусу. У всіх переривань є свій вектор переривання відповідно до таблиці векторів переривань. Переривання мають пріоритет відповідно до позиції їх вектора. Переривання з меншою адресою переривання мають більш високий пріоритет. Простір пам'яті введення-виведення містить 64 адреси з безпосередньою адресацією або може адресуватися як пам'ять даних, наступна за регістрами за адресами $ 20 - $ 5F. Крім того, Atmega8 має простір розширеного введення-виведення за адресами $ 60 - $ FF у статичному ОЗП, для доступу до якого можуть використовуватися тільки процедури ST / STS / STD і LD / LDS / LDD.

Поиск по сайту: |