|

|

|

Архитектура Астрономия Аудит Биология Ботаника Бухгалтерский учёт Войное дело Генетика География Геология Дизайн Искусство История Кино Кулинария Культура Литература Математика Медицина Металлургия Мифология Музыка Психология Религия Спорт Строительство Техника Транспорт Туризм Усадьба Физика Фотография Химия Экология Электричество Электроника Энергетика |

Статические параметры ЛЭ ⇐ ПредыдущаяСтр 2 из 2

Статические параметры определяют условия формирования и значения напряжений высокого и низкого уровней на выходе ЛЭ, его нагрузочную способность, потребляемую мощность при заданных напряжениях питания, нагрузке и температуре окружающей среды. К статическим параметрам ЛЭ относятся: · входные (U0вх, U1вх) и выходные (U0вых, U1вых) напряжения логического «0» и логической «1»; · входные (U0вх пор, U1вх пор) и выходные (U0вых пор, U1вых пор) пороговые напряжения логического «0» и логической «1»; · входные и выходные токи логического «0» и «1» (I0вх, I1вх, I0вых, I1вых); · токи потребления в состоянии логического «0» и «1» (I0пот, I1пот); · потребляемая мощность (Рпот). Входной ток ЛЭ задается для неблагоприятного режима работы в пределах допустимых температур окружающей среды и напряжения питания как для уровня «0» (I0вх), так и для уровня «1» (I1вх). Выходные токи (I0вых, I1вых) характеризуют нагрузочную способность ЛЭ. Втекающие токи имеют положительный знак, вытекающие – отрицательный. Помехоустойчивость определяется относительно этих токов. Поэтому увеличение коэффициента разветвления приводит к снижению помехоустойчивости. Мощность, потребляемая ЛЭ от источника питания, определяется как:

где Ui – напряжение i-го источника питания; Ii – ток в соответствующей цепи питания. Если потребляемая мощность зависит от выходного напряжения «0» (Р0пот) или «1» (Р1пот), то в качестве основного параметра используют среднюю потребляемую мощность Рпот = (Р0пот + Р1пот)/2. Для ЛЭ, потребляющих значительную мощность при переключении, средняя потребляемая мощность в технической документации задается в виде зависимости Рпот ср = f (Fимп), где Fимп – частота следования импульсов.

Семейства ИС

Логические элементы, выполненные на основе одной конструктивно-технологической реализации, образуют семейство схем. Широко распространены семейства микросхем ТТЛ, ТТЛШ, …, КМОП-логики. ТТЛ сокращенно означает транзисторно-транзисторная логика. Элементы этих схем построены на основе биполярных транзисторов. В схемах семейства КМОП применяются комплементарные МОП-транзисторы с каналами n- и p-типа.

Семейство ТТЛ-схем

Логические элементы схем этого семейства строятся на основе многоэмиттерных биполярных транзисторов (рисунок 1.8).

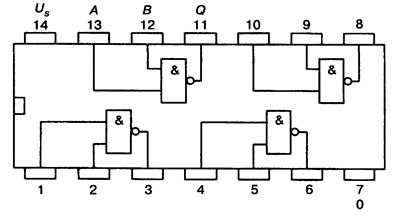

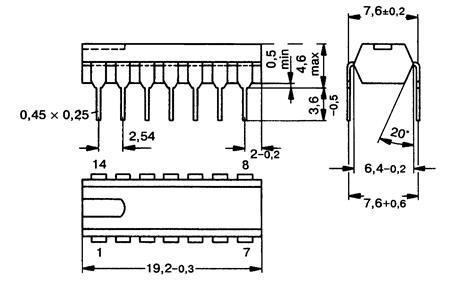

Если на входах А, В и С действует высокое напряжение, то транзистор Т1 работает в инверсном режиме (переход база-коллектор смещен в прямом направлении). Транзистор Т2 открыт, и на выходе Z будет низкое напряжение (примерно 0,2В). Если на одном их входов транзистора Т1 действует низкое напряжение, то транзистор Т1 работает нормально в режиме насыщения. Напряжение на его коллекторе падает примерно на 0,2В. Транзистор Т2 закрывается. На выходе Z будет высокое напряжение. Если один из входов многоэмиттерного транзистора Т1 «висит в воздухе», то он приравнивается к входу с высоким уровнем напряжения, так как такой вход не способен понизить напряжение в точке X схемы (рисунок 1.8) до 0,2В. ТТЛ-элементы выпускаются в виде интегральных микросхем. Например, микросхема SN7400 (отечественный аналог ЛА3 серии К155) содержит четыре элемента 2И-НЕ (рисунок 1.9). В основном ТТЛ-элементы выпускаются в DIP-корпусах (рисунок 1.10). В семейство ТТЛ-схем входят несколько серий ИМС. Все они имеют напряжение питания ± 5В и совместимы друг с другом.

Стандартная ТТЛ-серия К155 (7400) была первым промышленным стандартом.

В ТТЛШ-серии К531 (74S00) применение диодов и транзисторов Шоттки позволило сократить времена переключения схем. Маломощная ТТЛШ-серия К555 (74LS00) обладает более низкой потребляемой мощностью (таблица 1.1). Таблица 1.1 – Электрические характеристики ИМС ТТЛШ-серии К555 (74LS00)

В семействе ТТЛ-схем имеются все типы элементов, реализующих основные логические функции: · НЕ (элементы ЛН); · mИ (элементы ЛИ); · mИ-НЕ (элементы ЛА); · mИЛИ (элементы ЛЛ); · mИЛИ-НЕ (элементы ЛЕ); · mИ/mИЛИ-НЕ (элементы ЛР).

Поиск по сайту: |