|

|

|

Архитектура Астрономия Аудит Биология Ботаника Бухгалтерский учёт Войное дело Генетика География Геология Дизайн Искусство История Кино Кулинария Культура Литература Математика Медицина Металлургия Мифология Музыка Психология Религия Спорт Строительство Техника Транспорт Туризм Усадьба Физика Фотография Химия Экология Электричество Электроника Энергетика |

Назначение и классификация регистровСтр 1 из 2Следующая ⇒

Регистром называется типовой функциональный узел компьютера, предназначенный для приема, временного хранения, преобразования и выдачи многоразрядных двоичных слов. Регистры наряду со счетчиками и запоминающими устройствами являются наиболее распространенными последовательностными устройствами цифровой техники. Регистры обладают большими функциональными возможностями. Они используются в качестве управляющих и запоминающих устройств, генераторов и преобразователей кодов, счетчиков, делителей частоты, узлов временной задержки. Элементами структуры регистров являются синхронные триггеры D-типа либо RS- (JK)-типа с динамическим или статическим управлением. Один триггер – это простейший одноразрядный регистр (RG). В многоразрядных регистрах используют наборы или цепочки триггеров. В отличие от счетчиков регистры не имеют внутренних запрещающих обратных связей. Понятие "весовой коэффициент" к разрядам регистра, в отличие от счетчика, применимо не всегда. Однако, обозначение и нумерация входов и выходов аналогично счетчикам. Информационные входы обозначаются D1,D2, D3…(D0,D1, D2…), а выходы – Q1, Q2, Q3…(Q0, Q1, Q2 …). В наиболее общем случае регистры можно классифицировать по следующим признакам: · По функциональным свойствам регистры делятся на накопительные (регистры памяти, хранения) и сдвигающие. · По способу ввода/вывода информации регистры разделяются на параллельные, последовательные и комбинированные (параллельно-последовательные и последовательно-параллельные). · По направлению передачи (сдвига) информации – однонаправленные и реверсивные. · По способу управления записью регистры делятся на асинхронные и синхронные. · По числу тактов для записи слова – одно-, двух- и многотактные. · По числу линий для представления значения одного разряда слова (бита) – однофазные и парафазные; при однофазном представлении информации значение каждого разряда слова передается по одной линии связи (прямое или инверсное значение), а при парафазном – по двум линиям (одновременно передается прямое и инверсное значение разряда).

Регистры памяти

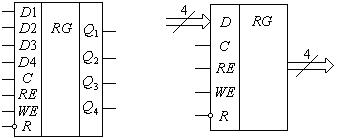

Регистры памяти – простейший вид регистров – хранят двоичную информацию. Это набор синхронных триггеров, каждый из которых хранит один разряд двоичного числа. Если регистр построен на триггерах-защелках, то такой регистр называют регистром-защелкой. Схема такого регистра представлена на рис. 8.1. Типовыми внешними связями регистра являются информационные входы Di, вход сигнала записи С (или загрузки синхронизации), вход гашения (установки в 0) R, выходы триггеров Qi, разрешение выхода (чтения) RE, разрешение приема информации (записи) WE. Возможны другие обозначение информационных и управляющих входов и выходов. Условное изображение регистра показано на рис. 8.2.

Рис. 8.1. Регистр памяти

Изображение по варианту а используется, когда нужно показать каждый вход и выход данных. Если же тракт данных рассматривается как единое, укрупненное понятие – шина данных, то используется обозначение, показанное на рис. 8.2, б.

а б

Рис. 8.2. Условное изображение регистра: а – с раздельными линиями по разрядам; б – с информационными линиями в виде шины

Часто регистры дополняются элементами отключения выходных шин. Тогда микросхема имеет дополнительный вход перевода в третье состояние EZ. Ввод (запись) и вывод (считывание) производится одновременно во всех разрядах при наличии разрешения WE или RE. С приходом очередного тактового импульса происходит обновление информации. Считывание информации может осуществляться в однофазном виде в прямом или обратном коде (с выходов В качестве подобных регистров могут быть использованы без дополнительных элементов многие синхронные триггеры: К155ТМ5, ТМ7, ТМ8, 564ТМ3, 555ТМ8 и др. Наращивание разрядности регистра достигается добавлением нужного числа триггеров, тактовые входы которых присоединяют к линии синхронизации. На рис. 8.3 представлен регистр К155ИР15 – регистр с тремя состояниями. Здесь D1 – D4 – информационные входы, С – синхронизирующий вход. Запись осуществляется по фронту 0,1 (

Рис. 8.3. Цоколевка регистра К155ИР15

Выпускаемые промышленностью регистры иногда объединяют на кристалле микросхемы с другими узлами, в паре с которыми регистры часто используются в схемах цифровой аппаратуры. Пример такого комплексного узла – микросхема многорежимного буферного регистра К589ИР12. Условное обозначение и структура регистра представлены на рис. 8.4. Микросхема состоит из восьми информационных D-триггеров, восьми выходных буферных устройств с тремя состояниями, отдельного D-триггера для формирования запросов на прерывание и гибкой схемы управления режимами работы регистра.

а б

Рис. 8.4. Условное обозначение (а) и функциональная схема (б) регистра ИР12

Микросхема имеет 24 вывода, из которых шестнадцать служат для ввода входных данных – DI1-DI8 и вывода выходных данных – DO1 - DO8. Управляющие сигналы: MD – выбор режима; CS1, CS2 – сигналы выбора кристалла; С – стробирующий сигнал; R – очистка (сброс); INT – сигнал прерывания, выдаваемый микропроцессору. Запись информации в регистр обеспечивается одной из следующих комбинаций управляющих сигналов: CS1∙CS2∙MD v C∙MD, где CS1, CS2 – входы выборки кристалла; когда CS1=0 и CS2=1, регистр выбирается; C – вход для подачи стробирующего сигнала при записи; MD – вход выбора режима, используется для определения тактирующего сигнала на входе С триггеров регистра (CS1∙CS2 при MD=1 или C при MD=0) и для управления состоянием выходного буфера. Чтение информации с регистра осуществляется одной из двух комбинаций входных сигналов: CS1, CS2 v MD. Формирование сигнала прерывания INT возможно при записи или чтении информации с регистра: CS1∙CS2 v C. Сброс запроса прерывания INT осуществляется сигналом очистки регистра R=0, или при CS1∙CS2=1 триггер прерывания устанавливается в 1. Часто регистры объединяются в блоки регистровой памяти – регистровые файлы. Такие микросхемы, могут быть объединены с входным дешифратором, позволяющим принимать входные данные в соответствующий регистр, выбираемый сигналами на адресных входах микросхемы. Объединяют регистры и с выходным мультиплексором MS, позволяющим выбирать содержимое соответствующего регистра. Пример схемы такого устройства представлен на рис. 8.5.

Рис. 8.5. Схема регистра общего назначения

Входы Di четырёх регистров подключены к общей входной шине данных DIN. Вход загрузки требуемого регистра выбирается дешифратором записи DCW на основании поступающего на вход DCW адреса записи WA (write address), т. е. кода номера загружаемого регистра. Запись данных, присутствующих на шине DIN, происходит по сигналу разрешения записи WE (write enable). Выходы регистров мультиплексором MS подключаются к выходной шине DOUT (data out). Номер регистра, с которого происходит чтение, определяет код адреса чтения RA (read address). Выдачу данных в шину DOUT разрешает сигнал RE (read enable). Поскольку дешифрация адреса записи и адреса чтения производится независимыми узлами (WA и RA), регистровая память может одновременно записывать данные в один регистр и читать из другого. Описанная структура использована в микросхеме 155РП1. Аналогичные, но более развитые структуры имеют регистровые памяти ИР11 и ИР12 серий К561 и К564, ИР26 155 серии и др. Микросхемы регистровой памяти легко наращиваются по разрядности и допускают наращивание по числу регистров. Они разработаны для построения блоков регистров общего назначения (РОН) и других специализированных блоков памяти небольшого объема, предназначенных для временного хранения исходных данных и промежуточных результатов в цифровом устройстве. Для памяти с большим числом регистров часто используют один дешифратор адреса и при записи и при чтении. Такую память называют памятью с произвольным доступом (по ЕСКД это RAM) – ОЗУ. В таких устройствах и ввод, и вывод данных часто осуществляется через одни и те же выводы корпуса микросхемы за счёт использования элементов с тремя состояниями. Пример реализации двунаправленной шины управления рассмотрен ранее (см. рис. 3.35, а). Здесь при наличии на входе Z сигнала низкого уровня (0) информация передается слева направо, при наличии высокого уровня – справа налево. Микросхемы ОЗУ малой ёмкости есть в составе распространённых серий. Они имеют входы адреса (Аi), данных (Di), режима W/R, выходы данных Qi, вход разрешения Е (BM, BK, CS – выбор кристалла). Примеры микросхем ОЗУ: 155РУ2 – 16*4 (16 слов по 4 разряда); 155РУ5 – 256*1; 564РУ2 – 256*1. Это статические ОЗУ. Они более быстродействующие, чем динамические.

Буферы данных

Кроме РОН в цифровых устройствах используют буферы данных, которые строят на основе регистровой памяти. В буфер записывают несколько слов по очереди (последовательно слово за словом). Для организации обычной очередности служит буфер типа “очередь”, или FIFO (first in – first out) первый вошел – первый вышел. Необходимость в таком буфере возникает, когда приемное устройство не успевает обрабатывать данные, которые поступают нерегулярно и иногда очень быстро. Если потери информации недопустимы, то между источником и приемником включается буфер FIFO, в котором хранится очередь слов, ожидающих обработки. Можно представить набор регистров в виде кольца (рис. 8.6). Часть регистров занята очередью, остальные – резерв.

Рис. 8.6. Диаграмма использования адресов регистра

Адрес записи при постановке в очередь задается счетчиком хвоста СТхв (рис. 8.7). По сигналу “поставить в очередь” на входе WE (разрешение записи – write enable) записываются данные с шины DI в тот регистр, номер которого хранится в счетчике хвоста очереди СТхв. Разрешение записи на соответствующий регистр поступает через дешифратор DCW. По срезу сигнала “поставить в очередь” выходной код счетчика хвоста увеличивается на 1, подготавливая адрес записи для очередного сигнала поставить в очередь. При поступлении сигнала извлечь из очереди на выходной шине D0 появляется слово, хранящееся в том регистре памяти, номер которого задан кодом счетчика головы очереди СТГОЛ. По срезу сигнала выходной код счетчика увеличивается на 1,

Рис. 8.7. Структура буферного регистра типа “очередь“

подготовив для выдачи следующее слово, стоящее теперь первым в очереди. Переполнение счетчика хвоста очереди осложнений не вызовет, т. к. после максимально возможного кода счетчика все единицы в нем автоматически появится код все нули. Очередь в своем кольце просто переползет через нулевую отметку счетчика. Так же со временем переползет и “голова”. В процессе нормальной работы очередь двигается в кольце значений адресов по часовой стрелке, хвостом вперед, удлиняясь или укорачиваясь в соответствии с флуктуациями активности передатчика. Перед началом работы оба счетчика сбрасываются в нуль. Однако могут возникнуть две особых ситуации, о которых буфер должен сигнализировать: первая – буфер полон, тогда в него нельзя больше записывать и нужно приостановить передатчик; вторая – буфер пуст, тогда из него нельзя брать данные, и нужно приостановить приемник. Обе ситуации возникают при равенстве показаний обоих счетчиков (головы и хвоста). Этот признак выявляет компаратор. Если коды на выходе счетчиков стали равны после очередного извлечения из очереди, то очередь иссякла и буфер пуст. Если они стали равны после очередной постановки в очередь, то буфер полон. Характер последнего обращения к буферу запоминается в RS-триггере. Сигналы, информирующие устройство управления об особых состояниях буфера, получаются как конъюнкция того или иного состояния триггера и признака равенства показаний счетчиков головы и хвоста. Другим, часто используемым буфером, является буфер типа “магазин”, или стек (stack), или буфер LIFO (last in – first out) – последний вошедший первым выходит. Один из вариантов реализации буфера представлен на рис. 8.8. В отличие от нормальной очереди здесь в качестве первого кандидата на обслуживание выбирается то слово, которое встало в очередь последним. Стековые структуры данных возникают в цифровых устройствах, когда процесс выполнения менее срочного задания прерывается более срочным и все данные, связанные с прерванной работой, засылаются на временное хранение в буфер типа “магазин”. Выполнение срочного задания может быть прервано поступлением сверхсрочного и т. д.

Рис. 8.8. Схема буферного регистра типа “магазин”

Основу буферного регистра “магазин” также составляют набор регистров памяти и счетчик адреса. В отличие от буфера “очередь” здесь счетчик должен быть реверсивным. Он должен уметь прибавлять 1 при поступлении команды “Заслать в стек (push)” и вычитать 1 при команде “Извлечь из стека (pop)”. Диаграмма использования адресов (рис. 8.9) показывает, что адрес, по которому производится засылка очередного слова в стек, всегда на единицу больше адреса регистра, из которого читается слово.

Рис. 8.9. Диаграмма использования адресов буферного регистра “магазин”

Последовательность операций в регистровой памяти при записи и считывании информации в простейшем случае следующая. При поступлении команды «Заслать в стек» происходит запись информации в регистр, на адрес которого указывает содержимое счётчика СТ. После этого происходит увеличение содержимого счётчика (адреса регистра) на 1. При поступлении команды «Извлечь из стека» содержимое счётчика (адрес регистра) уменьшается на 1. После этого происходит извлечение информации из регистра, на адрес которого указывает содержимое счётчика СТ (новый адрес регистра). Буферный регистр “магазин”, как и буфер типа “очередь”, также имеет два особых состояния: «буфер полон» и «буфер пуст». Эти состояния обнаруживаются по содержимому реверсивного счётчика СТ. Состоянию «буфер полон» соответствует содержимое счётчика 111…1, которое индицируется элементом И. При этом, запись в буфер запрещена. Состоянию «буфер пуст» соответствует содержимое счётчика 000…0, которое индицируется элементом НЕ-И. При этом считывание из буфера запрещено. Рассмотренный вариант аппаратной реализации регистра типа “магазин” не является единственным. Можно использовать другие виды памяти. Например, буфер типа “магазин” может быть реализован на основе сдвигающих регистров. Выбор варианта делается на основе оценки получаемых временных параметров и аппаратурных затрат.

Регистры сдвига

В рассмотренных регистрах не предусмотрена возможность сдвига информации, поэтому ввод и вывод “слова” в них осуществляется только в параллельном коде. Необходимо отметить также, что при выводе информации состояние триггеров не меняется. Следовательно, считывание слова из регистра может производиться многократно без разрушения информации. Чтобы иметь возможность осуществлять сдвиг информации, применяют сдвигающие регистры. Схема сдвигающего регистра на D-триггерах приведена на рис. 8.10.

а б

Рис. 8.10. Функциональная схема (а) и условное обозначение (б) сдвигового регистра

Регистр состоит из цепочки триггеров. Пусть ТТ0 – триггер младшего разряда, ТТ3 – триггер старшего. D-вход каждого триггера (кроме ТТ0) подключен к выходу соседнего (младшего) триггера. Когда на все объединенные С-входы триггеров поступает активный отрицательный фронт (спад) сигнала “сдвиг”, выход каждого триггера принимает состояние своего младшего соседа. Таким образом, информация, содержащаяся в регистре, сдвигается на один разряд в сторону старших триггеров, вправо. Выход D триггера ТТ0 принимает при этом состояние последовательного входа DS. Регистр загружается данными, последовательно поступающими по этому входу. Считывать данные, хранимые в RG, можно как в последовательном коде с выхода последнего разряда, так и в параллельном, сразу со всех разрядов. Сдвиг может производиться как влево, так и вправо. Далее рассмотрим кольцевые счетчики, которые строятся на базе сдвигающих регистров, а затем вернемся к конкретным сдвигающим регистрам.

Кольцевые счетчики В качестве счетчика может быть использован сдвигающий регистр, замкнутый в кольцо цепью обратной связи (рис. 8.11).

Рис . 8.11. Схема кольцевого счетчика на базе сдвигающего регистра

В этом регистре продвигается одна единица, которая при подаче очередного продвигающего импульса передается в следующую по порядку ячейку. Дойдя до конца регистра, единица записывается в первую ячейку и счет повторяется. Входной импульс с (тактирующий) в этом счетчике выполняет функции продвигающего. Число поступивших на вход импульсов фиксируется позицией единицы в регистре в данный момент времени. В таких счетчиках отсутствует последовательная передача сигнала переноса от ячейки к ячейке и поэтому задержка выходного импульса относительно входного оказывается незначительной. Количество двоичных ячеек должно быть равно коэффициенту счета (деления), при больших коэффициентах такой счетчик неэкономичен. Для существенного увеличения коэффициента счета при малых аппаратурных затратах счетчики соединяют последовательно (рис. 8.12). Если у одного счетчика коэффициент счета равен n, а у другого – m, то общий коэффициент счета будет равен произведению N = n * m.

Рис. 8.12. Последовательное соединение счетчиков

Продолжим далее рассмотрение сдвиговых регистров. В качестве первого примера сдвигового регистра рассмотрим микросхему К155ИР1 – четырехразрядный регистр сдвига с последовательным или параллельным вводом и параллельным выводом информации. Он может быть использован в качестве буферной памяти, элемента задержки на несколько тактов, преобразователя последовательного кода в параллельный и наоборот, делителя частоты, кольцевого распределителя импульсов, элемента арифметических устройств и т. п. Условное изображение приводится на рис. 8.13.

Рис. 8.13. Реверсивный сдвиговый регистр

С1, С2 – тактовые входы; V2 – выбор режима; V1 – для ввода информации в последовательном коде; D1-D4 для записи информации в параллельном коде; Q1-Q4 – четыре разряда выхода. Входы С1 и С2 для синхронизации от одного или двух генераторов. Срабатывание триггера по перепаду 1,0 импульсов на одном из входов С. Если на входе сигнал V2 = 0 – ввод последовательным кодом через V1 и сдвиг вправо, а тактовые импульсы подаются на С1. Сдвиг вправо при каждом перепаде 1,0 тактовых импульсов. Через 4 тактовых импульса информацию можно считать в параллельном коде. Ввод параллельным кодом производится при V2 = 1 по спаду импульса на входе С2. Входы V1 и С1 при этом блокированы и роли не играют. В этом же режиме V2 и С2 производится преобразование последовательного кода в параллельный со сдвигом влево. В этом случае информация идет от 4-го триггера к 3-му, от 3-го ко 2-му и т. д. Для этого выходы Q4, Q3, Q2 соединяют со входами D3, D2, D1 соответственно. Информация в последовательном коде поступает через вход D4 при каждом перепаде С2 с 0 на 1. Таблица состояний регистра 155ИР1 приведена ниже.

Во избежание сбоев смена состояний V2 должна происходить только при С1 = С2 = 0. Последовательным соединением n микросхем можно получить 4-n разрядный регистр с преобразованием параллельного кода в последовательный и наоборот. Микросхема К155ИР13 – универсальный 8-ми разрядный регистр сдвига с большими функциональными возможностями – представлена на рис. 8.14.

Регистр может работать в следующих режимах (табл. 8.2): – последовательный ввод информации со сдвигом вправо; - последовательный ввод со сдвигом влево; - параллельный ввод; - хранение; - установка нулей (сброс).

Рис. 8.14. Универсальный восьмиразрядный сдвиговый регистр

Информационные входы последовательного ввода: DR – при сдвиге вправо; DL – при сдвиге влево; D1¸D8 – параллельный ввод; С – тактовый вход; S1, S0 – для выбора режима; R – для установки триггера в 0; Q1¸Q8 – выходы.

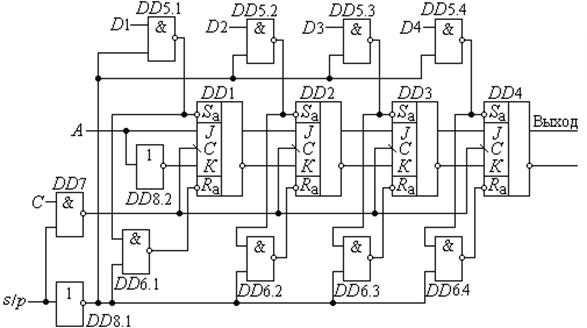

Далее приведена схема регистра сдвига с параллельным и последовательным вводом информации и последовательным ее выводом (рис. 8.15). Режим работы регистра определяется сигналом на входе s/p (последовательно–параллельно). Допустим, сигнал на этом входе имеет уровень 1. На выходе инвертора DD8 будет 0, который закроет логические элементы DD5.1–DD5.4 и DD6.1–DD6.4 и создаст тем самым на асинхронных входах триггеров Sa и Ra уровни 1, разрешающие синхронное действие. Входы D1–D4 для параллельного ввода информации при этом заблокированы. Тактовые импульсы на входе обеспечат синхронный ввод информации в последовательном коде (со входа А) и также сдвиг ее вправо. За счет инверсии тактовых импульсов элементом DD7 тактирование происходит по фронту 0,1 (а не по срезу).

Рис. 8.15. Схема реверсивного регистра

Когда на входе s/p 0 элемент DD7 заперт, тактирование триггеров прекращается. Сигнал на общих входах элементов DD5.1–DD5.4 и DD6.1–DD6.4 становится 1, вследствие чего каждый из этих элементов для сигналов на шинах параллельного ввода D1–D4 служит инвертором. Под воздействием входных сигналов параллельного ввода выходы соответствующих триггеров примут те же состояния – Qi = Di. С появлением на входе s/p 1 (разрешение тактирования) информация, введенная в параллельном коде, с каждым тактовым импульсом будет сдвигаться на один разряд и выдаваться в последовательной форме, т. е. произойдет преобразование информации параллельного вида в последовательный. Если в такой схеме сделать выводы с выхода каждого JK-триггера, то можно будет вводить и выводить информацию в параллельном и в последовательном коде и преобразовывать из последовательного кода в параллельный, и наоборот.

Поиск по сайту: |

) или в парафазном виде.

) или в парафазном виде. ), Q1 – Q4 – прямые выходы, Е1, Е2 – разрешающие входы. Запись возможна при Е1 = Е2 = 0 (если на одном из входов Е логическая 1, то это режим хранения информации). Входы ЕZ1,EZ2 – перевод в 3-е состояние, R – установка в 0 (высоким уровнем): с приходом 1 на вход R все триггеры устанавливаются в 0. При вводе информации на входах Е1, Е2 и R должен быть 0. Если на EZ (любом) логическая 1 – выходы отключаются. Более подробные сведения о режимах работы микросхемы можно посмотреть, например, в [12, 13].

), Q1 – Q4 – прямые выходы, Е1, Е2 – разрешающие входы. Запись возможна при Е1 = Е2 = 0 (если на одном из входов Е логическая 1, то это режим хранения информации). Входы ЕZ1,EZ2 – перевод в 3-е состояние, R – установка в 0 (высоким уровнем): с приходом 1 на вход R все триггеры устанавливаются в 0. При вводе информации на входах Е1, Е2 и R должен быть 0. Если на EZ (любом) логическая 1 – выходы отключаются. Более подробные сведения о режимах работы микросхемы можно посмотреть, например, в [12, 13].