|

|

|

Архитектура Астрономия Аудит Биология Ботаника Бухгалтерский учёт Войное дело Генетика География Геология Дизайн Искусство История Кино Кулинария Культура Литература Математика Медицина Металлургия Мифология Музыка Психология Религия Спорт Строительство Техника Транспорт Туризм Усадьба Физика Фотография Химия Экология Электричество Электроника Энергетика |

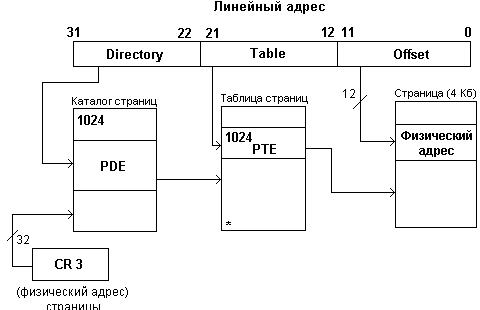

Базовый механизм страничной переадресации ⇐ ПредыдущаяСтр 6 из 6

Механизм защиты страниц различает 2 уровня привилегий: 1 уровень – пользователь 2 уровень – супервизор Пользователю соответствует уровень привилегий 3. Супервизору – 0, 1, 2. Для того, чтобы работать со страницей увеличенного размера используется режим PSE (Page Size Extention). При таком режиме выпадает Table и таблица страниц. Кроме этих режимов страничной переадресации возможна переадресация в режимах для страниц 4 Кб и 2 Мб (размер страниц всегда одинаковый). 6. Виртуализация прерываний. В многозадачной системе с разделяемыми устройствами внешние прерывания изначально обрабатываются ОС, которая определяет, к какой задаче относится каждое конкретное прерывание. Задача, которая должна обрабатывать аппаратные прерывания может получать их как в реальном виде, так и в виртуальном. Если приложению передаются реальные прерывания, то использование виртуальной памяти с подкачкой страниц становится мало возможным, чтобы избежать подкачки страниц по аппаратным прерываниям, обработчики прерываний должны располагаться в ядре ОС, постоянно присутствующем в памяти. Если задача находится в непрерывном состоянии, то ОС может сообщить о прерывании только после перехода в прерываемое состояние. Такие прерывания называются виртуальными. 7. В защищенном режиме возможно использовать режим виртуального 8086 процессора.

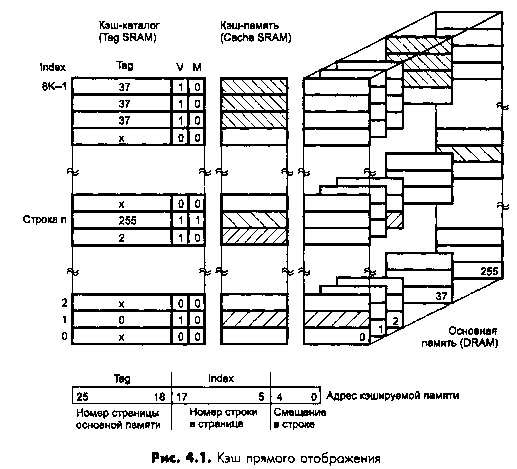

20 Архитектура памяти. Основная память компьютеров реализуется на относительно медленной динамической памяти (DRAM), обращение к ней приводит к простою процессора — появляются такты ожидания (waitstates). Статическая память (SRAM), построенная, как и процессор, на триггерных ячейках, по своей природе способна догнать современные процессоры по быстродействию и сделать ненужными такты ожидания (или хотя бы сократить их количество). Разумным компромиссом для построения экономичных и производительных систем явился иерархический способ организации оперативной памяти. Идея заключается в сочетании основной памяти большого объема на DRAM с относительно небольшой кэш-памятью на быстродействующих микросхемах SRAM. 21 Принципы кэширования. Кэш является дополнительным быстродействующим хранилищем копий блоков информации из основной памяти, вероятность обращения к которым в ближайшее время велика. Кэш не может хранить копию всей основной памяти, поскольку его объем во много раз меньше основной памяти. Кэш-контроллер должен обеспечивать когерентность — согласованность данных кэш-памяти с данными в основной памяти, если обращение к этим данным производиться не только процессором, но и другими активными адаптерами, подключенными к шинам (PCI, VLB, ISA и т. д.). Следует также учесть, что процессоров может быть несколько, и у каждого может быть свой внутренний кэш. Существуют две основные политики записи данных из кэша в основную память: сквозная запись WT (WriteThrough) и обратная запись WB (WriteBack). 1. Сквозная запись– выполнение каждой операции записи одновременно и в Кэш и в основную память. «+»: простая реализация, легко обеспечивает целостность данных; «-»: низкая эффективность, т.к. процессору приходится ждать записи в основную память. 2. Обратная запись– данные из кэш в основную память записываются только после заполнения кэш памяти.«+»: уменьшается количество операций записи на шине основной памяти эффективный алгоритм. «-»: более сложная реализация, поддержка системной платой кэширования с обратной записью требует обработки дополнительных интерфейсных сигналов; Управление заполнением кэша возможно и на аппаратном, и на программном уровнях. Процессор позволяет кэшировать любую область физической памяти. Программно можно управлять кэшируемостью каждой страницы памяти — запрещать единичным значением бита PCD (PageCacheDisable) в таблице. Общее программное управление кэшированием осуществляется посредством бит управляющего регистра CRO: CD (CacheDisable) и NW (NoWriteThrough). Возможны следующие сочетания бит регистра: CD=1, NW=1 —установки такого значения выполнить очистку кэша, кэш будет полностью отключен. Если перед установкой этого сочетания бит кэш был заполнен, а очистка не производилась, кэш превращается в «замороженную» область статической памяти. CD=1, NW=0 — заполнение кэша запрещено, но сквозная запись разрешена. Этот режим может использоваться для временного отключения кэша, после которого возможно его включение без очистки. CD=0, NW=1 — запрещенная комбинация (вызывает отказ общей защиты). CD=0, NW=0 — нормальный режим работы со сквозной записью. 22Кэш прямого отображения. В кэш-памяти прямого отображения адрес памяти, по которому происходит обращение, однозначно определяет строку кэша, в которой может находиться требуемый блок. Архитектура прямого отображения подразумевает, что каждая строка кэша может отображать из любой страницы кэшируемой памяти только соответствующую ей строку. Поскольку объем основной памяти много больше объема кэша, на каждую строку кэша может претендовать множество блоков памяти с одинаковой младшей частью адреса (смещением внутри страницы). Одна строка в определенный момент может, естественно, содержать копию только одного из этих блоков.

Номер (адрес) строки в кэш-памяти называется индексом (index). Тег несет информацию о том, какой именно блок занимает данную строку (то есть старшая часть адреса или номер страницы). Память тегов должна иметь количество ячеек, равное количеству строк кэша, а ее разрядность должна быть достаточной, чтобы вместить старшие биты адреса кэшируемой памяти, не попавшие на шину адреса кэш-памяти. «+»: простая аппаратная реализация применяется в кэш второго уровня в совершенных платах. «-»: если в процессе выполнения программы процессору поочередно будут требоваться блок памяти смещения относительно друг друга на величину кратную размеру страницы, то будет происходить сплошная череда кэш промахов.

Рис. - Кэш прямого отображения. 23 Наборно-ассоциативный кэш. Наборно-ассоциативная архитектура кэша позволяет каждому блоку кэшируемой памяти претендовать на одну из нескольких строк кэша, объединенных в набор (set). Можно считать, что в этой архитектуре есть несколько параллельно и согласованно работающих каналов прямого отображения, где контроллеру кэша приходится принимать решение о том, в какую из строк набора помещать очередной блок данных. В простейшем случае каждый блок памяти может помещаться в одну из двух строк (TwoWaySetAssociativeCache). Такой кэш должен содержать два банка памяти и тегов (рис. 40).

Рис. 40. Двухканальный наборно-ассоциативный кэш. Наборно-ассоциативная архитектура широко применяется для первичного кэша современных процессоров. Объем кэшируемой памяти определяется так же, как и в предыдущем варианте, но здесь будет фигурировать объем одного банка (а не всего кэша) и разрядность относящихся к нему ячеек тега. 24 Ассоциативный кэш. У полностью ассоциативного кэша любая его строка может отображать любой блок памяти, что существенно повышает эффективность использования его ограниченного объема. При этом все биты адреса кэшированного блока, за вычетом бит, определяющих положение (смещение) данных в строке, хранятся в памяти тегов. В такой архитектуре для определения наличия затребованных данных в кэш-памяти требуется сравнение со старшей частью адреса тегов всех строк, а не одной или нескольких, как при прямом отображении или наборно-ассоциативной архитектуре. Естественно, последовательный перебор ячеек памяти тегов отпадает — на это может уйти слишком много времени. Остается параллельный анализ всех ячеек, что является сложной аппаратной задачей, которая пока решена только для небольших объемов первичного кэша в некоторых процессорах. Применение полностью ассоциативной архитектуры во вторичном кэше пока не предвидится 25 Шины расширения. Типы. Характеристики. Применение. Шины расширения предназначены для подключения различных адаптеров, периферийных устройств расширяющих возможности компьютерной системы. К ним относятся: ISA, EISA, PCI. Развитием шины PCI является порт AGP, предназнач. для подключения мощных графических адаптеров. Шины расширения системного уровня позволяют устанавливаемым модулям расширения максимально использовать системные ресурсы ПК: пространство памяти, ввода/вывода, прерывания, команды DMA. При этом необходимо обеспечить точное соответствие протоколам шины (включая жесткие частотные и нагрузочные параметры и временные диаграммы).Нарушение этих требований может заблокировать работу, как конкретного устройства, так и системы в целом.

Поиск по сайту: |