|

|

|

Архитектура Астрономия Аудит Биология Ботаника Бухгалтерский учёт Войное дело Генетика География Геология Дизайн Искусство История Кино Кулинария Культура Литература Математика Медицина Металлургия Мифология Музыка Психология Религия Спорт Строительство Техника Транспорт Туризм Усадьба Физика Фотография Химия Экология Электричество Электроника Энергетика |

Схема простейшего триггера, построенного на инверторах

Простейшая схема, позволяющая запомнить двоичную информацию может быть построена на 2-х инверторах, охваченных положительно обратной связью. В этой схеме может быть только 2 состояния – на входе Q присутствует логическая единица и на выходе инверсного Q присутствует логический ноль. Если логическая единица присутствует на выходе Q, то на инверсном выходе будет присутствовать логический 0, который после очередного инвертирования подтверждает уровень логической единицы на выходе Q. Если на выходе Q присутствует логический ноль то на инверсном выходе Q будет присутствовать логическая единица. Такая ситуация будет до тех пор, пока есть питание.

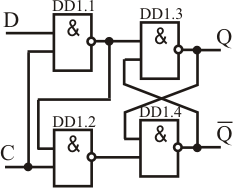

D-триггер Самый распространённый, занимает промежуточное положение между RS-триггером и JK. Помимо всех общих для триггеров входов R и S (установка и сброс) он имеет информационный вход D и один тактовый вход С.

Базовые концепции конвейера Скорость выполнения программы зависит от многих факторов. Одним из способов его повышения является внедрение передовых технологий при проектировании и изготовлении процессоров и модулей основной памяти. Эта технология была направлена как на повышение быстродействия функциональных устройств, так и на совершенствование их архитектуры с целью увеличения количества параллельно выполняемых операций. Второй метод предлагает увеличение количества операций, выполняемых за 1 секунду. При этом время отводимое на 1 операцию остаётся неизменным.

Роль Кэш памяти Каждая ступень конвейера должна выполнять команды за 1 такт. Это условие соблюдается, если такт достаточно велик. В случае когда блоком конвейера для решения задачи требуется различное время такт времени выполнения становится равен самой продолжительной задачи. Блок, работа которого завершается бездействует до конца такта. По этому конвейеризация наиболее эффективна в том случае, когда для решения стоящих в разных степенях задач необходимо примерно одинаковое время.

Триггер - это устройство, обладающее двумя состояниями устойчивого равновесия. Триггер еще можно назвать устройством с обратными связями. На рисунке изображена схема триггера на логических элементах ИЛИ-НЕ.

Рис. 1 Схема простейшего RS-триггера Такая схема называется асинхронным RS-триггером. Первый (сверху) выход называется прямым, второй - инверсным. Если на оба входа (R и S) подать лог. нули, то состояние выходов определить невозможно. Триггер установится как ему заблагорассудится, т. е. в произвольное состояние. Допустим, на выходе Q присутствует лог. 1, тогда на выходе не Q (Q с инверсией) обязательно будет лог. 0. И наоборот. Чтобы установить триггер в нулевое состояние (когда на прямом выходе лог. 0, на инверсном - лог. 1) достаточно на вход R подать напряжение высокого уровня (про уровни напряжений). Если высокий уровень подать на вход S, то это переведет его в состояние 1, или как говорят, в единичное состояние (на прямом выходе лог. 1, на инверсном - лог. 0). И в том, и в другом случаях напряжение соответствующего уровня может быть очень коротким импульсом - на грани физического быстродействия микросхемы. То есть, триггер обладает двумя устойчивыми состояниями, причем эти состояния зависят от ранее воздействующих сигналов, что позволяет сделать следующий вывод - триггер является простейшим элементом памяти. Буквы R и S по-буржуйски set - установка, reset - сброс (предустановка). На рис. 2 RS-триггер показан в "микросхемном исполнении".

Рис. 2 RS-триггер в интегральном исполнении RS-триггер можно соорудить и на элементах И-НЕ, как показано на рисунке 3. Такая конструкция встречается довольно часто.

Рис. 3 RS-триггер на логических элементах И-НЕ Принцип работы такой же, как у триггера на элементах ИЛИ-НЕ, за исключением инверсии управляющих сигналов, т. е. установка и сброс триггера производится не лог. 1, а лог. 0. Другими словами, входы такого триггера инверсные. В описанных триггерах изменение состояния происходит сразу после изменения состояния на входах R и S. Поэтому такие триггеры называются асинхронными. Если схему асинхронного триггера немного дополнить, то получим вот такое:

Рис. 4 Синхронный RS-триггер на логических элементах И-НЕ В таком триггере вводится дополнительный вход С, называемый тактовым или синхронизирующим. Изменение состояний триггера происходит при подаче сигналов лог. 1 на входы R и S и последующим воздействием на вход С тактового (синхронизирующего) импульса. Если на тактовый вход импульс не воздействует, то состояние триггера не изменится. Другими словами, изменение состояния триггера происходит под действием синхроимпульса, поэтому такие триггеры называются синхронными. D-триггер D-триггер отличается от синхронного RS-триггера тем, что у него только один информационный вход D. D-триггер показан на рисунке 5.

Рис. 5 D-триггер на логических элементах И-НЕ Если на вход D подать логическую единицу, затем на вход С подать импульс, то на выходе Q (прямой выход) установится лог. 1. Если на вход D подать лог. 0, на С импульс, то на Q установится лог. 0. Т. е. D-триггер осуществляет задержку информации, поступающей на вход D. При чем эта информация хранится в D-триггере, пока не придет следующий бит (0 или 1) информации. По сути это ячейка памяти. Если вход D замкнуть с инверсным выходом, то останется только один вход С. При подаче на вход С импульса триггер переключится, т. е. если на выходе был лог. 0, то станет лог. 1. При следующем импульсе триггер снова переключится, т. е. лог. 1 сменится лог. 0. Таким образом, триггер осуществляет деление частоты входных импульсов на 2 (ведь уровень сигнала на выходе меняется в два раза реже). В таком режиме D-триггер называют счетным или Т-триггером. Этот режим (режим деления частоты) используется довольно широко. Нетрудно заметить, что для RS-триггера (рис. 1) существует запрещенная комбинация, когда на оба входа поданы лог. 1, на его выходах также устанавливаются лог. 1 и триггер перестает выполнять свои функции (зависает). Поэтому придумали так называемый JK-триггер. У него три входа - J, K, C. Вход J вместо R, вход К вместо S, С так и остается - синхронизацией. Если на вход J подана лог. 1, на К - лог. 0 или наоборот, то он работает как синхронный RS-триггер, если на оба входа J и К поданы лог. 1, то он работает как счетный Т-триггер.

Поиск по сайту: |