|

|

|

Архитектура Астрономия Аудит Биология Ботаника Бухгалтерский учёт Войное дело Генетика География Геология Дизайн Искусство История Кино Кулинария Культура Литература Математика Медицина Металлургия Мифология Музыка Психология Религия Спорт Строительство Техника Транспорт Туризм Усадьба Физика Фотография Химия Экология Электричество Электроника Энергетика |

Выполнение машинной команды

Регистры общего назначения 32-х битные регистры общего назначения eax, ebx, ecx, edx, esi, edi, ebp и esp могут хранить следующие типы данных: · Операнды для логических и арифметических операций · Операнды для расчета адресов · Указатели на ячейки памяти Многие команды используют конкретные регистры для хранения своих операндов. Например, команды обработки текстовых строк используют содержимое регистров ecx, esi и edi в качестве операндов. Основные случаи использования регистров общего назначения:

В регистрах, оканчивающихся на x, можно обращаться к младщим 16-ти битам (ax, bx, cx и dx соответственно), которые в свою очередь можно разделить на старший байт (ah, bh, ch и dh) и младший (al, bl, cl и dl) и работать с ними, как с регистрами длиной 8 бит. Регистры-указатели esp (указатель вершины стека) и ebp (базовый регистр), а также индексные регистры esi (индекс источника) и edi (индекс приемника) допускают только 32-битное обращение.

2) Регистры сегментов Регистры сегментов (cs, ds, ss, es, fs и gs) хранят 16-ти битные дескрипторы сегментов. Дескрипторы сегментов - это специальные указатели, определяющие расположение сегмента в памяти. Регистры флагов Этот регистр представляет собой набор флагов, устанавливаемых или сбрасываемых по результатам выполняемых команд. Флаг - это переменная длиной 1 бит, используемая в командах условного перехода. Если значение этой переменной равно 1, то считается, что флаг установлен, если 0 – сброшен. Существует несколько видов флагов.

· Флаг знака (sf) устанавливается при единичном значении старщего бита результата - признаке отрицательного числа 4) Регистры приема, хранения, выдачи кодов Эти регистры являются самыми распространенными регистрами в компьютере, т.к. для преобразования информации перед любой вычислительной операцией необходимо иметь ту информацию, которая позволяет выполнить код операции в формате команды. Регистр приема, хранения, выдачи кодов строится на основе двух компонентов: RS-синхронного триггера и логического элемента «И»

13) Счетчик – устр-во, предназнач. для подсчёта числа импульсов, поступивших на его вход и хранение результата в виде кода. Классификация счётчиков: - по направлению счёта: а) суммирующие б) вычитающие в) реверсивные - по коэффициенту пересчёта: а)двоичные б)недвоичные Асинхронный суммирующий двоичный счётчик:

Таблица истинности 2-го счётчика:

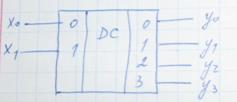

14) Комбинационные схемы. Дешифратор. Дешифратор- устр-во для расшифровки сообщения и перевода содержащейся в нём информации на язык (код) воспринимающей системы. Это комбинационные схемы с несколькими входами и выходами, преобразующие код, подаваемый на входы в сигнал на одном из выходов. На выходе дешифратора появляется логическая единица, на остальных — логические нули, когда на входных шинах устанавливается двоичный код определённого числа или символа, то есть дешифратор расшифровывает число в двоичном, троичном или k-ичном коде, представляя его логической единицей на определённом выходе. Число входов дешифратора равно количеству разрядов поступающих двоичных, троичных или k-ичных чисел. Число выходов равно полному количеству различных двоичных, троичных или k-ичных чисел этой разрядности.

15) Мультиплексор- схема, к-рая обеспечивает подключение одного из информационных входов к выходу. 4 входа D0, D1, D2, D3 – явл. информационными, а 2 входа Х0 и Х1- управляющими. Сигнал одного из инф-ых входов передаётся на выход У, причём комбинация сигналов на управл-их входах указывает, с какого именно. Обозначение мультиплексора: в англоязычной лит-ре:

согласно ГОСТ:

Табл. истинности М. на 4 входа:

16) Сумматор - комбинационная схема, предназначенная для выполнения арифметических операций над двоичными числами. Особенностью поразрядного сложения в двоичной системе является формирование сигнала переноса. Таблица истинности функции поразрядного сложения, которая формирует значение в данном разряде и сигнал переноса в следующий разряд:

Сумматоры классифицируют по различным признакам. В зависимости от системы счисления различают: · двоичные; · двоично-десятичные (в общем случае двоично-кодированные); · десятичные; · прочие (например, амплитудные). По количеству одновременно обрабатываемых разрядов складываемых чисел:

· многоразрядные. По числу входов и выходов одноразрядных двоичных сумматоров: · четвертьсумматоры, характеризующиеся наличием двух входов, на которые подаются два одноразрядных числа, и одним выходом, на котором реализуется их арифметическая сумма; · полусумматоры, характеризующиеся наличием двух входов, на которые подаются одноимённые разряды двух чисел, и двух выходов: на одном реализуется арифметическая сумма в данном разряде, а на другом — перенос в следующий (более старший разряд); · полные одноразрядные двоичные сумматоры, характеризующиеся наличием трёх входов, на которые подаются одноимённые разряды двух складываемых чисел и перенос из предыдущего (более младшего) разряда, и двумя выходами: на одном реализуется арифметическая сумма в данном разряде, а на другом — перенос в следующий (более старший разряд). По способу представления и обработки складываемых чисел многоразрядные сумматоры подразделяются на: · последовательные, в которых обработка чисел ведётся поочерёдно, разряд за разрядом на одном и том же оборудовании; · параллельные, в которых слагаемые складываются одновременно по всем разрядам, и для каждого разряда имеется своё оборудование.

Четвертьсумматор имеет в два раза меньше выходов и в два раза меньше строк в таблице истинности по сравнению с полным двоичным одноразрядным сумматором. Таблица истинности четвертьсумматора

С

Условное обозначение четвертьсумматора

Полусумматор имеет два входа Ai, Bi и два выхода Si и Pi (рис.3). На входы Ai и Bi последовательно подаются уровни, соответствующие разрядам суммируемых двоичных чисел. Полусумматор формирует перенос Pi в следующий разряд, но не может учитывать перенос из предыдущего разряда, поэтому он и называется полусумматором Таблица истинности полусумматора

Схема полусумматора

Условное обозначение полусумматора Полный сумматор строится из двух полусумматоров, на его дополнительный вход поступает сигнал переноса от предыдущей схемы суммирования. Первый из них используется для сложения входных двоичных сигналов Аi и Bi. С помощью второго полусумматора учитывается входной сигнал переноса Рn-1. Таблица истинности полного сумматора

Схема полного сумматора

Условное обозначение полного сумматора

17) Функциональная схема ЭВМ. Принципы Фон-Неймана. 1) Программное управление работой ЭВМ. 2) Принцип условного перехода. 3) Принцип хранимой программы. 4) Принцип использования двоичной системы счисления. 5) Принцип иерархичности запоминающих устройств. Арх. ЭВМ, построенной по принципу Фон-Неймана:

АЛУ – вып. арифм. и логич. операции над двоичными числами. УУ – координирует работу всех устр-тв ЭВМ путём подачи на них управляющих сигналов. ОЗУ – память, к-рая хранит ту информацию, с к-рой ПК работает непосредственно в данное время. ВЗУ – Постоянная память, используемая для долговременного хранения информации. УВВ (устр-ва ввода-вывода) – предназнач. для перевода информации из внутр. представления внутри ЭВМ в форму, понятную человеку, и обратную.

18)

19)Системная шина. - основная интерфейсная система компьютера, обеспечивающая сопряжение и связь всех его устройств между собой. Системная шина включает в себя:

Шины могут быть синхронными (осуществляющими передачу данных только по тактовым импульсам) и асинхронными (осуществляющими передачу данных в произвольные моменты времени). Системная шина обеспечивает три направления передачи информации:

Часто помимо шины общего назначения, позволяющей подключать большое число самых разнообразных устройств, в ПК применяются локальные шины, специализирующиеся на обслуживании небольшого количества устройств определенного класса, преимущественно видеосистем. Шины могут использовать различные схемы арбитража, то есть способа совместного использования шины несколькими устройствами. Основными схемами арбитража являются централизованная схема, при использовании которой передачей информации по системной шине управляет одно из подключённых устройств или специально выделенный для этого узел, называемый арбитром шины, и децентрализованная (распределенная) схема, в которой арбитр шины не используется. Шины характеризуются разрядностью и частотой. Важнейшими функциональными характеристиками системной шины являются количество обслуживаемых ею устройств и ее пропускная способность, то есть максимально возможная скорость передачи информации. Пропускная способность шины зависит от ее разрядности и тактовой частоты, на которой шина работает. Разрядность или ширина шины (bus width) —количество битов, которое может быть передано по шине одновременно. Тактовая частота шины (bus frequency) — частота, с которой передаются последовательные биты информации по линиям связи. В ПК применяются шины ISA, EISA, MCA, VLB, PCI, PCI-E, PCMCIA (CardBus) и AGP. Параллельная и последовательная шины отличаются способом передачи данных. В параллельной шине данные передаются одновременно по нескольким "проводникам". Параллельное подключение устройств позволяет экономить линии шин данных и адреса, но требует от устройств, чтобы они могли, кроме перевода линий шин в высокое и низкое логические состояния, еще и отключаться от шины во избежание конфликтов. Выбор активного устройства производится путем докодирования состояния линий шины адреса, а направление передачи по параллельной шине определяется сигналами чтения и записи. В последнее время наблюдается стремление разработчиков аппаратуры перейти от параллельных шин к последовательным. Объясняется это сложностями синхронизации обмена по параллельным шинам на высоких частотах - если физические проводники, реализующие шину, будут иметь различие по длине, на высоких частотах это приведет к расхождению фронтов сигналов на разных проводниках, увеличению времени, необходимого для установления переходных процессов перед подачей сигналов записи или чтения и, тем самым, ограничению максимальной скорости передачи и быстродействия устройств. Последовательные шины реализуются более простыми физическими средствами, но требуют более сложных устройств для передачи и приема, поскольку требуется преобразование информации из параллельной формы в последовательную и обратно, а при передаче формирование избыточных кодов для надежной передачи и коррекции ошибок, если они возникают. Последовательные шины более просты механически, более устойчивы к помехам и в перспективе имеют более широкие перспективы для перехода на высшие скорости обмена. В ПК применяются шины ISA, EISA, MCA, VLB, PCI, PCI-E, PCMCIA (CardBus), AGP, PCI Express. Рассмотрим самые распространенные:

Выполнение машинной команды

Поиск по сайту: |

Табл. истинности:

Табл. истинности:

хема четвертьсумматора

хема четвертьсумматора