|

|

|

Архитектура Астрономия Аудит Биология Ботаника Бухгалтерский учёт Войное дело Генетика География Геология Дизайн Искусство История Кино Кулинария Культура Литература Математика Медицина Металлургия Мифология Музыка Психология Религия Спорт Строительство Техника Транспорт Туризм Усадьба Физика Фотография Химия Экология Электричество Электроника Энергетика |

Побудова універсальних логічних модулів (УЛМ) за допомогою MS

Опорний конспект Тема 1.3. Типові функціональні вузли комбінаційних цифрових пристроїв. Дешифратор (Decoder)

Дешифратором називається функціональний вузол комп’ютера призначений для перетворення кожної комбінації вхідного двійкового коду в керуючий сигнал лише на одному із “m” виходів. Цей сигнал називається активним. Якщо дешифратор має n входів і m=2n – виходів, то такий дешифратор є повним. Якщо число виходів менше 2n, то дешифратор називають неповним. Умовно графічне позначення дешифратора приведене на рис. 1.

Рис. 1. УГП дешифратора: а) на функціональних схемах; б, в, г) на принципіальних схемах.

У схему дешифраторів вбудовуються один, два або три стробуючих (дозволяючих) входи, наприклад Е рис. 1 або Вказати рівні сигналів:

Виходи DC активні Виходи DC пасивні Е1= ____________ Е1= ____________ Е2= ____________ Е2= ____________

Рис. 2

Використання входів дозволу

Рис. 3. Рис. 4. В комп'ютерах дешифратори використовують для виконання таких операцій: ü дешифрації коду операції, записаного в регістр команд процесора, що забезпечує вибір потрібної мікропрограми; ü перетворення коду адреси операнда в команді в керуючі сигнали вибору заданої комірки пам'яті в процесі записування або читання інформації; ü забезпечення візуалізації на зовнішніх пристроях; ü реалізації логічних операцій та побудови мультиплексорів і демультиплексорів. Завдання для самоконтролю Задача 1. Використовуючи таблицю істинності для дешифратора 2→4 записати логічні вирази.

F1=_______________________________________ F2=_______________________________________ F3=_______________________________________ F4=_______________________________________ Задача 2.Аналізуючи рис.4 кожну комбінацію вхідного двійкового коду (х1,х2,х3), при

Задача 3. Який вихід дешифратора буде активним на рис. 5. Вказати на виходах DC активні та пасивні рівні сигналів.

Рис. 5.

Задача 4. Вказати двійковий код на інформаційних входах та рівні сигналів на стробуючих входах, а також на виходах дешифратора, для активізації 9, 12, 5, 14 виходів, рис. 6.

а) активний 9 вихід б) активний 12 вихід в) активний 5 вихід г) активний 14 вихід

Рис. 6.

Задача 5. Запишіть логічну функцію в МДНФ, яку виконує наступна електрична принципова схема на рис. 7а, для чого спочатку дати відповіді на запитання.

Рис. 7a. DD1 – KP1533ИД7, DD2 – KP1533ЛА2

Дати відповіді на запитання 1. На виході дешифратора (рис.7а) активним рівнем буде ______________, а пасивним _______________. 2. Елемент позначений DD2 виконує функцію __________________ ____________________________________________________________________. 3. Входи елемента DD2 підключені до Uж, чому? ________________ ____________________________________________________________________ 4. Входи 1, 2, 4 (DD1) мають назву _____________________________, а входи Е1, Е2, Е3 (DD1) мають назву ____________________________________. 5. Записати логічні вирази кожного виходу дешифратора. 0-________, 1-__________, 2-__________, 3-__________, 4-__________, 5-__________, 6-__________, 7-__________. 6. Записати логічний вираз ____________________________________________________________________ 7. Як буде працювати DC (DD1), якщо вхід Е3 заземлити? ________ ____________________________________________________________________

Самостійна робота Задача 1. Побудувати схему відтворення логічних функцій

Задача 2.Вивчити форми сигналів які надходять на інформаційні входи ІС КР1533ИД3, та вказати рівні сигналів на входах Е1,Е2, та який вихід буде активним в моменти часу t3, t15, t8, t6, t16.

Записати номер виходу та рівень сигналу на цьому виході. t3____;(___), t15____;(___), t8____;(___), t6____;(___), t16____;(___).

Задача 3. Побудувати 32-х канальний дешифратор використовуючи УГП дешифраторів 2→4 та 3→8. Кожен дешифратор має один вхід дозволу. Дати визначення ЦП декодера та відповіді на наступні запитання. 1. Скільки потрібно дешифраторів 2→4? ___________________________ 2. Скільки потрібно дешифраторів 3→8? ___________________________ Шифратор (Coder) Шифратором називається функціональний вузол комп’ютера, призначений для перетворення вхідного m-розрядного універсального коду у вихідний n-розрядний двійковий позиційний код. Умовні графічні позначення шифраторів на схемах показані на рис. 8.

Рис.8. УГП шифратора: а) на функціональних схемах; б) на принципових схемах. Шифратор має певну кількість входів, причому в кожен момент часу тільки один з них може бути активізованим, в результаті чого шифратор формує двійковий код, структура якого залежить від того, який із входів був у стані збудження. Задача. Визначити стан виходів шифратора на рис. 9, якщо вхід 5 активізований, а на рис. 10 активізований 6 вхід. Вказати рівні сигналів на входах та виходах шифратора.

У цифрових пристроях шифратори використовують для таких операцій: ü Перетворення унітарного вхідного коду у вихідний двійковий позиційний код; ü Введення десяткових даних з клавіатури; ü Позначення старшої одиниці в слові; ü Передача інформації між різними пристроями при обмеженому числі ліній зв’язку. Одне з основних застосувань шифратора — введення даних з клавіатури, наприклад, десяткових цифр. Натискання клавіші з десятковою цифрою 0, 1, …, 9 мають приводити до передачі в цифровий пристрій двійково-десяткового коду цієї цифри. Для цього використовується неповний шифратор "з 10 в 4". Шифратори, які при одночасному натисканні декількох клавіш виробляють код тільки старшої цифри, називаються пріоритетними. Пріоритетні шифратори, які призначені для пошуку старшої (лівої) одиниці в слові та формування на виході двійкового номера шуканого розряду, називаються покажчиками старшої одиниці. Їх застосовують у пристроях нормалізації чисел з плаваючою комою, в системах з пріоритетним обслуговуванням запитів на переривання роботи комп'ютера. Контрольні запитання 1. Чим шифратор відрізняється від дешифратора? ___________________ __________________________________________________________________ __________________________________________________________________ 2. Чим відрізняється пріоритетний шифратор від звичайного? _________ __________________________________________________________________ __________________________________________________________________ __________________________________________________________________. Мультиплексор. Мультиплексором називається функціональний вузол комп’ютера, призначений для підключення одного зі вхідних каналів D0, D1…Dn на виход Q під керівництвом відповідного кода адресного простору А0, А1…Аm-1. Зв'язок між числом інформаційних (n) і адресних (m) входів визначається співвідношенням n=2m. Таким чином, мультиплексор реалізує керовану передачу даних від кількох вхідних ліній в одну вихідну. Умовно графічне позначення мультиплексорів показано на рис. 11.

Рис. 11. УГП мультиплексорів: а) на функціональних схемах; б) на принципових схемах; в) ІС КР1533КП7, де С – вхід стробування.

Дозволяючий (стробуючий) вхід керує одночасно всіма інформаційними входами незалежно від стану адресних входів. Наявність дозволяючого входу розширює функціональні можливості мультиплексора: ü даючи можливість синхронізувати його роботу з роботою інших вузлів, а також цей вхід використовується для нарощування розрядності мультиплексорів, якщо потрібно більше інформаційних входів, ніж їх є у даному мультиплексорі. ІС мультиплексорів відрізняються числом входів, способом адресації, наявністю входів дозволу, прямими та інверсними виходами. Логіка роботи 4-х канального мультиплексора наведена в таблиці 1.

Таблиця 1.

Мультиплексор виконує функцію:

В інтегральному виконанні мультиплексори випускають на чотири, вісім або шістнадцять входів (каналів). Каскадування дозволяє реалізувати комутацію довільного числа вхідних ліній на базі серійних мікросхем мультиплексорів меншої розрядності.

Приклад побудовимультиплексорана 16 каналів на основі типових чотиривходових мультиплексорів показано на рис. 12.

Рис. 12.

Входи стробування також можна використовувати для збільшення входів. На рис. 13 зображено 16 канальний комутатор, виконаний на двох 8 - канальних мультиплексора. Проаналізуйте роботу схеми, та запишіть у таблицю 2 рівні сигналів на адресних входах, та виходах Q (

Рис.13.

Таблиця 2.

Завдання для самоконтролю 1. Опишіть як побудувати перетворювач паралельного коду в послідовний на базі КР1533КП7, якщо число паралельних входів дорівнює 16. ________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________ 2. Як подати адресні сигнали на входи А1, А2, А3 мультиплексора КР1533КП7, рис 11в, якщо вхідні сигнали треба комутувати в такій послідовності: 3,5,1,7. ________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________

3. Побудувати схему MS «32→1» за допомогою КР1533КП7

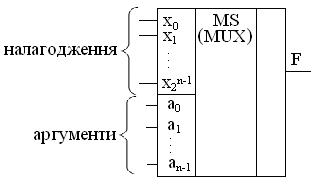

Побудова універсальних логічних модулів (УЛМ) за допомогою MS. УЛМ на основі MS відносять до пристроїв, які налагоджуються до розв’язання будь-якої задачі. Універсальність їх полягає у тому, що для заданого числа аргументів можна налагодити УЛМ на будь-яку функцію. Для цього потрібно змінити значення його входів. На адресні входи потрібно подавати аргументи функції, а на інформаційні входи сигнали налагодження.

Рис. 14.

Логічні блоки на MS використовуються у сучасних СВІС програмної логіки, які випускаються відомими фірмами.

Завдання для самоконтролю 1. Побудувати схему УЛМ для виконання логічних функцій АБО, І-НЕ, І, АБО-НЕ за допомогою MS (4→1).

Демультиплексор Демультиплексором називається функціональний вузол комп'ютера, призначений для комутації (перемикання) сигналу з одного інформаційного входу D на один з n інформаційних виходів. Номер виходу, на який в кожний такт машинного часу передається значення вхідного сигналу, визначається адресним кодом A0,A1,A2,…,Am-1. Адресні входи m та інформаційні виходи n пов'язані співвідношенням n = 2m або m = log2n. Демультиплексор виконує функцію, обернену функції мультиплексора. Стосовно мультиплексорів і демультиплексорів користуються також терміном "селектори" даних. В умовних графічних позначеннях (рис.15) функція демультиплексора позначається буквами DMX.

Рис. 15. УГП демультиплексорів: а) на функціональних схемах; б) на принципових схемах; в) типове з’єднання з мультиплексором. Демультиплексори використовують для таких операцій: • комутації як окремих ліній, так і багаторозрядних шин; • перетворення послідовного коду в паралельний; • реалізації логічних функцій та інших. Демультиплексори часто позначають: "1 →n". Каскадування дозволяє реалізувати комутацію одного вхідного сигналу на довільне число вихідних ліній на базі серійних мікросхем меншої розрядності. Нехай потрібно реалізувати демультиплексування вхідного сигналу на п вихідних ліній, що визначаються m-розрядним адресним кодом, на базі типових мікросхем меншої розмірності виду "1 →n1".

Рис. 16. Каскадування мультиплексорів

ІС дешифратора можна використовувати як демутьтиплексор. Наприклад. Розглянемо ІС КР1533ИД3 (рис. 17) один із його входів дозволу С1 можна використовувати як інформаційний вхід, а другий С2 як вхід дозволу (або навпаки), та входи (1, 2, 4, 8) – як адресні. Відповідний двійковий код на входах (1, 2, 4, 8) дозволяє сигналу проходити від інформаційного входу до визначеного виходу.

1, 2, 4, 8 – адресні входи Рис. 17. Задача 1. Який сигнал поступає на інформаційний вхід, якщо відомо які сигнали на виходах пристрою, та маємо графіки А1=f(t), А2=f(t).

Задача 2.Який двійковий код буде на адресних входах, якщо вихід 13 є активним (в стані збудження), рис 17. Вказати рівні сигналів на адресних входах та на активному виході.

Поиск по сайту: |

рис. 2. при наявності дозволу

рис. 2. при наявності дозволу  дешифратор працює, при його відсутності всі виходи дешифратора пасивні.

дешифратор працює, при його відсутності всі виходи дешифратора пасивні.

дає змогу досить просто будувати схему дешифратора більшої розрядності вхідного коду. З’єднання двох три розрядних дешифраторів дає декодування чотирозрядного коду, показано на рис. 3. Інтегральна мікросхема КР1533ИД4 – це здвоєний дешифратор 2→4 з інверсними виходами. Цю ІС дешифратора можна використовувати для побудови 8-ми канального дешифратора, рис. 4.

дає змогу досить просто будувати схему дешифратора більшої розрядності вхідного коду. З’єднання двох три розрядних дешифраторів дає декодування чотирозрядного коду, показано на рис. 3. Інтегральна мікросхема КР1533ИД4 – це здвоєний дешифратор 2→4 з інверсними виходами. Цю ІС дешифратора можна використовувати для побудови 8-ми канального дешифратора, рис. 4.

, вказати порядковий номер виходів, позначивши їх через уі(і=0,1,2,…,7).

, вказати порядковий номер виходів, позначивши їх через уі(і=0,1,2,…,7).

________________________ ____________________________________________________________________

________________________ ____________________________________________________________________  та

та  , використовуючи DC (3→8) та елемент АБО. Спочатку запишіть повні логічні вирази.

, використовуючи DC (3→8) та елемент АБО. Спочатку запишіть повні логічні вирази.

- без стробуючого . входу

- без стробуючого . входу - зі стробуючим входом

- зі стробуючим входом

), якщо на входи 2, 12, 4, 3, 10 надходять відповідні рівні сигналів.

), якщо на входи 2, 12, 4, 3, 10 надходять відповідні рівні сигналів.

Приклад 1. Побудувати УЛМ для реалізації логічної функції по mod2 використовуючи мультиплексор 4→1.

Приклад 1. Побудувати УЛМ для реалізації логічної функції по mod2 використовуючи мультиплексор 4→1.

Приклад 2.На входи налагодження можна перенести будь-який аргумент. Розглянемо який саме аргумент доцільно переносити до сигналів налагодження. Найкраще слід переносити аргументи, які мають мінімальну кількість входження у терми функції, в цьому випадку будуть максимально використовуватися як внутрішні логічні ресурси MS, а для сигналів налагодження збільшується кількість констант, що і є благоприємним для схемної реалізації УЛМ. Розглянемо логічну функцію

Приклад 2.На входи налагодження можна перенести будь-який аргумент. Розглянемо який саме аргумент доцільно переносити до сигналів налагодження. Найкраще слід переносити аргументи, які мають мінімальну кількість входження у терми функції, в цьому випадку будуть максимально використовуватися як внутрішні логічні ресурси MS, а для сигналів налагодження збільшується кількість констант, що і є благоприємним для схемної реалізації УЛМ. Розглянемо логічну функцію

Приклад 3.Можна побудувати УЛМ використовуючи додаткові логічні схеми, якщо вихідна функція більш ніж від одного аргументу.

Приклад 3.Можна побудувати УЛМ використовуючи додаткові логічні схеми, якщо вихідна функція більш ніж від одного аргументу.

- інформаційний вхід

- інформаційний вхід - вхід дозволу

- вхід дозволу