|

|

|

Архитектура Астрономия Аудит Биология Ботаника Бухгалтерский учёт Войное дело Генетика География Геология Дизайн Искусство История Кино Кулинария Культура Литература Математика Медицина Металлургия Мифология Музыка Психология Религия Спорт Строительство Техника Транспорт Туризм Усадьба Физика Фотография Химия Экология Электричество Электроника Энергетика |

Процессорный модуль на БИС 1810 ⇐ ПредыдущаяСтр 2 из 2

На основеМП 1810 можно центральные процессоры для простых микроконтроллеров и вычислительные модули мультипроцессорных систем. При построении простых микроконтроллеров МП 1810 чаще всего работает в минимальном режиме, а архитектура всего микроконтроллера использует однопользовательскую системную шину. В такой конфигурации процессор состоит из МП КР1810ВМ86, системного генератора КР1810ГФ84 и БИС магистрального интерфейса КР580ИР82/83, КР580ВА86/87 или КР1810ИР82/83 и КР1810ВА86/87, предназначенных для обеспечения требуемой нагрузочной способности. В схеме на рис. 1.15 интерфейс адресной шины реализован на буферных регистрах КР580ИР82, в которые записывается информация с выходов AD0-AD15, A16-A19 МП 1810ВМ86 по сигналу STB в такте Т1 и хранится там в течение всего машинного цикла. Интерфейс шины данных реализован на шинных формирователях КР580ВА86. Информация о данных поступает в формирователи по сигналу

Селектор адреса памяти.Архитектурная особенность МП 1810 такова, что область ПЗУ удобнее располагать в области самых верхних адресов (с адреса FFFFFH и вниз) объемом не менее 64Кбайт. Область ОЗУ можно располагать в любом месте адресного пространства. Простой способ выбора области памяти ¾ использование старшего разряда адреса, который поделит область памяти на две части (рис. 3а, 4а).

а б

а б

б а Рис. 4 Используя два старших разряда адреса можно разделить объем памяти на четыре области по 256 Кбайт (рис. 3б). Самое простое решение при построении селектора адреса ¾ использование только логических элементов (рис. 4б). В такой схеме ПЗУ находится всомой нижней (А19=0, А18=0) и в самой верхней (А19=1, А18=1) области адресов, а ОЗУ занимает среднюю область адресов (А19=0, А18=1, А19=1, А18=0).

Рис.5

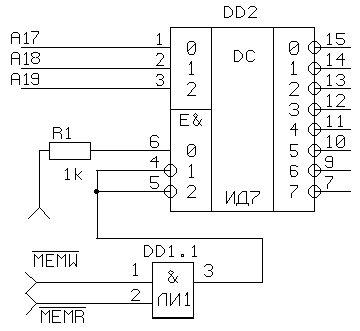

Селектор адреса портов ввода/вывода.Построение селектора адреса портов не отличается от построения селекторов адреса памяти. В них тоже используются дешифраторы. Адресное пространство портов может занимать 256 адресов (при 8 разрядном адресе) или 65536 адресов (при 16 разрядном адресе). Все адресное пространство разбивается на блоки (окна), в которые подключаются порты ввода/вывода. Минимальный размер окна ¾ 4 адреса (практически все периферийные БИС требуют 4 адреса). При делении адресного пространства на окна используются старшие адреса А15...А9 (А7...А3) (рис. 6). Также как и селектор адреса памяти, селектор адреса портов ввода/вывода должен срабатывать только при обращении к портам. Для этого в качестве сигналов синхронизации можно использовать сигналы

Поиск по сайту: |

с выходов AD0-AD15 МП КР1810ВМ86 в такте Т2-Т3. Мультиплексор К555КП11 формирует раздельные сигналы чтения/записи ЗУ и ВУ.

с выходов AD0-AD15 МП КР1810ВМ86 в такте Т2-Т3. Мультиплексор К555КП11 формирует раздельные сигналы чтения/записи ЗУ и ВУ. (Рис. 2)

(Рис. 2)

Рис. 3

Рис. 3

При увеличении количества областей памяти (при уменьшении их объема) селекторы адреса можно реализовать на микросхемах дешифраторов (рис. 5). Например использование дешифратора К555ИД7 (рис. 5) даст возможность получить 8 зон объемом 128 Кбайт (на микросхему подаются адреса А19...А17), а дешифратор К555ИД13 ¾ 16 зон по 64 Кбайта (на микросхему подаются адреса А19...А16). Более мелкое деление нецелесообразно, т.к. минимальный объем сегмента МП 1810 64 Кбайт. Селектор адреса памяти должен срабатывать только при обращении к памяти, для этого необходимо кроме адресов на дешифратор подавать сигналы

При увеличении количества областей памяти (при уменьшении их объема) селекторы адреса можно реализовать на микросхемах дешифраторов (рис. 5). Например использование дешифратора К555ИД7 (рис. 5) даст возможность получить 8 зон объемом 128 Кбайт (на микросхему подаются адреса А19...А17), а дешифратор К555ИД13 ¾ 16 зон по 64 Кбайта (на микросхему подаются адреса А19...А16). Более мелкое деление нецелесообразно, т.к. минимальный объем сегмента МП 1810 64 Кбайт. Селектор адреса памяти должен срабатывать только при обращении к памяти, для этого необходимо кроме адресов на дешифратор подавать сигналы  (рис. 5), которые будут разрешать работу дешифратора во время обращения к памяти.

(рис. 5), которые будут разрешать работу дешифратора во время обращения к памяти. .

. рис. 6

рис. 6