|

|

|

Архитектура Астрономия Аудит Биология Ботаника Бухгалтерский учёт Войное дело Генетика География Геология Дизайн Искусство История Кино Кулинария Культура Литература Математика Медицина Металлургия Мифология Музыка Психология Религия Спорт Строительство Техника Транспорт Туризм Усадьба Физика Фотография Химия Экология Электричество Электроника Энергетика |

Лабораторная работа № 3. ИЗУЧЕНИЕ ОДНОКРИСТАЛЬНЫХ МИКРОПРОЦЕССОРОВ НА ПРИМЕРЕ МИКРОПРОЦЕССОРА КР1810

ИЗУЧЕНИЕ ОДНОКРИСТАЛЬНЫХ МИКРОПРОЦЕССОРОВ

Цель работы:

Изучить организацию 16-ти разрядного микропроцессора КР1810ВМ86. Ознакомится с его системой и форматом команд, способами адресации. Научится организовывать вычислительный процесс, используя возможности микропроцессора.

1. Теоретическая часть 1.1. Общие сведения о МПКР1810. Микропроцессор КР1810ВМ86 является аналогом микропроцессора Intel8086, который является базовым для ПЭВМ семейства IBM PC. Архитектура данного МП имеет возможность выполнения арифметических и логических операций над 8-, 16-, 32- и 64-разрядными словами, операций над последовательностями (цепочками) байт и слов, а также операций над двоично-кодированными десятичными данными. В 16-разрядном АЛУ реализуются операции умножения и деления с фиксированной запятой. Микропроцессор содержит 135 базовых инструкций, которые с учетом многочисленных режимов адресации увеличивается до нескольких сотен. Микропроцессор имеет практически неограниченное число уровней прерывания. Прямо адресуемая область памяти составляет 1 Мбайт – 20-ти разрядная шина адреса. Для организации связи с памятью и УВВ используется интерфейс типа И41. Программы составленные для МП К580, относительно легко переделать для выполнения на МП К1810, так как система команд МП К580 представляет собой подмножество команд МП К1810 и обеспечивается программная совместимость снизу вверх. Микропроцессор имеет одно напряжение питания +5В однофазную синхронизацию с частотой 5 МГц и выпускается в 40-контактном керамическом корпусе с двусторонними выводами. Кристалл МП с геометрическими размерами 5,5X5,5 мм содержит около 29000 транзисторов. Структура МП КР1810 На рис. 3.1 показана схема МП, которое состоит из двух автономных частей: устройство сопряжения с шиной (УСШ), организующее опережающую выборку команд из памяти и формирующее очередь выбранных байт последовательности команд, и операционное устройство, извлекающее команды из очереди и реализующее предписанные командами операции в 16-разрядном АЛУ.

Рис.3.1. Структурная схема МП КР1810

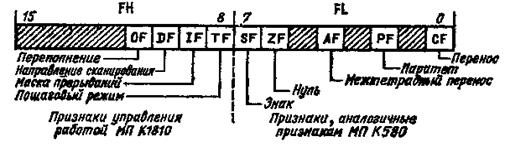

В состав УСШ входят 6-байтная очередь команд, счетчик команд, четыре сегментных регистра и сумматор. В состав операционного устройства (ОУ) входят блок регистров общего назначения (в том числе два регистра-указателя и два индексных регистра), арифметико-логическое устройство (АЛУ) и регистр признаков F. Устройство управления МП осуществляет управление УСШ, ОУ и, кроме того, периферийным оборудованием системы, обеспечивая обмен данными с использованием механизмов квитирования, прерывания и прямого доступа к памяти. Устройство сопряжение с шиной Устройство сопряжения с шиной обеспечивает формирование 20-разрядного физического адреса памяти, выборку команд и операндов из памяти, организацию очередности команд и запоминание результатов выполнения команд в памяти В состав УС входят шесть 8-разрядных регистров очереди команд (РОК), четыре 16-разрядных сегментных регистра (CS, DS, SS, ES), 16-разрядный регистр адреса команд (1P), 16-разрядный регистр обмена (РО) и 16-разрядный сумматор адреса (СМА), управление шиной (УШ). Устройство сопряжения готово выполнить цикл выборки слова из памяти всякий раз, когда в очереди освобождаются по меньшей мере 2 байта. Шина адреса в этом микропроцессоре имеет 20 разрядов и с ее помощью можно адресовать пространство 1 Мб (220байт - 1Мб). Но, так как, число разрядов регистров процессора меньше числа разрядов ША, то с помощью одного регистра нельзя полностью задать адрес физической ячейки памяти. В этом случае пользуются так называемой «сегментацией», которая подразумевает использование двух регистров: в первом регистре находится адрес начала сегмента, во втором - внутрисегментное смещение. Сегмент - область памяти, максимальный размер которой 64 Кб (216- 65536 байт - 64 Кб). Начальный адрес сегмента должен находиться по адресу, номер которого кратен 1610 (т.е. если этот адрес представить в виде шестнадцатеричного числа, то в младшем разряде этого числа будет 0). Внутрисегментное смещение - расстояние от начала сегмента до нужной нам ячейки памяти. Операционное устройство При создании данного МП разработчики стремились сохранить программную совместимость с 8-разрядным МП (К580), и это оказало влияние на нерегулярность структуры ОУ и специализацию многих внутренних регисторов. Хотя прямой программной совместимости не достигнуто, но все регистры МП К580 имеют аналоги в блоке РОН МП К1810, и в результате этого программы МП К580 легко трансформировать для выполнения в этом 16-разрядном МП. В состав блока РОН входят четыре 16-разрядных регистра АХ, ВХ, СХ и DX, допускающих независимую адресацию старших (Н) и младших (L) половин. Такая организация адресации регистров позволяет прямо обрабатывать как байты, так и двухбайтные слова. Все регистры блока РОН на общих основаниях участвуют в выполнении арифметических и логических операций, представляя операнды и фиксируя результат выполнения операции. Наряду с этим в системе команд МП имеется множество команд, которые специализируют некоторые РОН: регистр АХ выполняет функции аккумулятора; с ним связаны операции умножения, деления, преобразования и десятичной коррекции. Он участвует во всех операциях В В в качестве или источника или приемника информации. Регистр AL соответствует аккумулятору МП К580, а регистр АН является его расширением; регистр ВХ используется как источник базового адреса и в некоторой степени соответствует регистровой паре HL микропроцессора К580; регистр СХ используется в качестве счетчика в командах сдвигов и зацикливания, а также при операциях с цепочками байт; регистр DX неявным образом адресуется в командах умножения и деления и, кроме того, содержит адрес порта ВВ при косвенно-регистровой адресации. Четыре 16-разрядных указательных и индексных регистра (SP, ВР, SI, DI) предназначены для хранения внутрисегментных смещений, обеспечивая косвенную адресацию и динамичные вычисления исполнительных адресов. Эти же регистры могут участвовать в выполнении арифметических и логических операций над двухбайтными словами. Указательные регистры SP (стека) и ВР (базы) предназначены для упрощения доступа к данным в текущем сегменте стека, но не в сегменте данных. Если сегмент специально не определен, то смещения SP и ВР по умолчанию относятся к текущему сегменту стека. Индексные регистры SI (источника) и DI (приемника) содержат смещения, которые по умолчанию относятся к текущему сегменту данных. Эти четыре регистра специализируются в некоторых командах, что находит отражение в их названиях и аббревиатурах. Формат 16-разрядного регистра признаков F показан на рис. 3.2. Его младший байт FL полностью соответствует регистру признаков МП К580: CF — перенос, PF — чет/нечет (в байте), AF — межтетрадный перенос (в байте), ZF — нуль, SF — знак. Кроме перечисленных признаков, которые фиксируют особенности результата последней арифметической или логической операции в МП К1810, имеет место признак переполнения OF.

Рис. 3.2. Формат регистра признаков

В дополнение к этому в регистре признаков F фиксируются некоторые признаки, предназначенные для управления вычислительным процессом в МП: признак направления DF определяет направление сканирования массива данных в операциях с цепочками (при DF==0 выполняется инкрементирование, а при DF=1 де-криментирование содержимого регистра-указателя массива); признак прерывания IF используется в механизме маскирования прерываний (при IF=1 прерывания разрешены, т.е. МП воспринимает запросы на прерывание); признак прослеживания TF, будучи установленным в единичное состояние, переводит МП в режим исполнения программы по командам (пошаговый режим), что необходимо при отладке программ. Стек- область памяти для временного хранения данных. Регистр SS указывает сегмент, a регистр SP - наибольшее допустимое смещение в сегменте стека Здесь используется косвенная адресация с помощью указателя SP; при записи элемента в стек (а это всегда слово, т.е. 16 бит) происходит автоматическое уменьшение SP на 2, а при извлечении - увеличение на 2. Адрес последнего включенного элемента в стек называется вершиной. Стек используется для хранения состояния процессора (в него заносят содержимое всех его программно-доступных регистров), а также для передачи параметров в процедуры. Микропроцессор Intel 8086 имеет возможность реагировать на внешние события посредством вызова одной из набора программ обслуживания. Событие, вызывающее переход на такую программу, называется прерыванием. Возможна обработка двух классов прерываний: внешних и внутренних. Внешние прерывания инициируются аппаратным сигналом на выводах микропроцессора INT, поступающим от периферийных устройств, а внутренние прерывания возникают при выполнении программ. Независимо от типа прерывания, возникающие при этом действия одинаковы: · завершается текущая команда, если ею не является команда НLТ или WAIT; · определяется тип прерывания N; · текущее состояние регистра признаков (PSW), CS и IP включается в стек; · биты условий сбрасываются; · передается управление по вектору N; · выполняются процедуры прерывания; · извлекается из стека IP, CS, PSW. Способы адресации Для микропроцессора Intel 8086 режимы адресации делятся на два класса: для данных и для переходов. Непосредственная, при котором операнд длиной 8 или 16 бит является частью команды. Прямая, при котором 16-битовый исполнительный адрес (ИА) операнда является частью команды. Регистровая, при котором операнд может находиться в одном из регистров: АХ, АН, AL, ВХ, ВН, BL, СХ, СН, CL, DX, DH, DL, ВР, SP. SI, DI. Регистрово-косвенная, при котором ИА операнда находится в одном из указанных регистров: [ВХ], [ВР], [SI], [DI]. В зависимости от используемых регистров, эта адресация называется базовая и индексная. Регистровая относительная, при котором ИА операнда вычисляется как сумма 8- или 16-битового смещения и содержимого базового ([ВХ],[ВР]) или индексного ([SI], [DI]) регистра. Базово - индексная, при котором ИА определяемся как сумма содержимого базового ([ВХ], [ВР]) и индексного ([SI],.[DI]) регистров. Относительная базово-индексная (комбинированная), при котором ИА равен сумме адреса, который вычисляется в базовом индексном режиме, и 8-или 16-битового смещения. Примеры ассемблерных мнемоник для различных режимов адресации приведены ниже (команда MOV AX, OPR пересылает OPR в регистр АХ, где OPR - операнд): MOV АХ, 55 ; Непосредственный MOV AX, VAR ; Прямой MOV АХ, ВХ ; Регистровый MOV АХ, [ВХ] ; Регистровый косвенный MOV АХ, [ВХ-10] ; Регистровый относительный MOV AX, [BP+Dl] ; Базовый индексный MOV AX, [BP+SI+4] ; Относительный базовый индексный При выполнении программ микропроцессор реализует такую последовательность действий: 1. Выбирает команду по адресу, содержащемуся в регистре IP. 2. Загружает команду в программно-недоступный регистр и дешифрирует ее с одновременным увеличением содержимого регистра IP для адресации следующей команды. При необходимости изменить последовательность выполнения команд программист использует команды передачи управления. Для таких команд (условные и безусловные переходы, вызовы процедур) существуют четыре режима адресации переходов. Внутрисегментный прямой переход, при котором адрес команды в сегменте кода определяется как сумма содержимого регистра IP и 8' или 16-битового смещения. В командах условных переходов допускается использовать только 8-битовое смещение. Внутрисегментный косвенный переход используется только в командах безусловного перехода, при этом содержимое регистра IP заменяется 16-битовым значением выбранного регистра или ячейки, указывается в любом из режимов адресации данных, кроме непосредственного. Межсегментный прямой переход, при котором содержимое регистров IP и С заменяется двумя словами, располагающимися непосредственно в команде. Межсегментный косвенный переход, при котором содержимое регистров IP и С заменяется двумя последовательно расположенными в памяти словами. Эти слова могут быть указаны в любом режиме адресации данных, кроме непосредственного и регистрового. Примеры ассемблерных мнемоник для различных режимов адресации переходов: JMP LAB ; внутрисегментный прямой переход JMP [ВХ] ; внутрисегментный косвенный переход JMP FAR PTR LAB ; межсегментный прямой переход JMP DWORD |BX] ; межсегментный косвенный переход Как было указано выше, микропроцессор КР1810ВМ86 генерирует 20-разрядный физический адрес, состоящий из 16-разрядного адреса сегмента и 16-разрядного смещения. При этом используются следующие правила адресации: · выборка команд происходит только по адресу, заданному регистрами IP и CS; · регистр SP применяется только как смещение по отношению к регистру SS; · если регистр ВХ является базовым, то по умолчанию операнд находится в сегменте данных и для вычисления физического адреса используется регистр DS; · если регистр ВР является базовым, то по умолчанию операнд находится в сегменте стека и для вычисления физического адреса используется регистр SS; · если используются оба регистра - базовый и индексный, то операнд находится в сегменте, на который указывает базовый регистр; · если используется только индексный регистр, то операнд находится в сегменте данных, на который указывает регистр DS.

Поиск по сайту: |