|

|

|

Архитектура Астрономия Аудит Биология Ботаника Бухгалтерский учёт Войное дело Генетика География Геология Дизайн Искусство История Кино Кулинария Культура Литература Математика Медицина Металлургия Мифология Музыка Психология Религия Спорт Строительство Техника Транспорт Туризм Усадьба Физика Фотография Химия Экология Электричество Электроника Энергетика |

Обработка экспериментальных данных. Описание экспериментальной установки

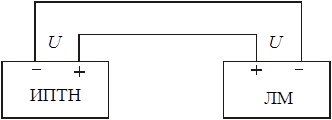

Описание экспериментальной установки Экспериментальная установка включает в свой состав источник постоянного тока с регулируемым напряжением, цифровой вольтметр и лабораторный макет с расположенными на нем логическими элементами (рисунок 6.1) и формирователями логических уровней - низкого «0» и высокого «1».

Рисунок 6.1 Рабочее задание 1 Ознакомиться с экспериментальной установкой. Закрепить макет на стенде. 2 Подключить лабораторный макет ЛМ к источнику постоянного тока с регулируемым напряжением ИПТР, соблюдая полярность, как показано на рисунке 6.2. Установить выходное напряжение источника питания U = 6В.

Рисунок 6.2 3 Подключая вольтметр поочередно к выходу формирователей логических уровней измерить напряжения, соответствующие логическому нулю U0 и логической единице (равное напряжению питания ИМС логических элементов) U1=Uп. Зафиксировать полученные значения. 4 Используя проводник, подать на вход элемента НЕ (инвертора) сигнал, соответствующий уровню логического «0» (x=0). С помощью вольтметра измерить выходное напряжение Uвых и определить, какому логическому уровню Y оно соответствует. Результаты занести в таблицу 6.1. Таблица 6.1

5 Подать на вход инвертора уровень логической «1» (x=1) и произвести измерение согласно п.4. 6 Измерить и зафиксировать напряжения на входе Uвх и выходе Uвых элемента НЕ при неподключенном (неиспользуемом, свободном) входе. Определить и занести в таблицу 6.2 состояние выхода Y инвертора. Таблица 6.2

7 Экспериментально составить таблицу истинности для логического элемента ИЛИ (дизъюнктора). Для этого, задавая комбинации логических уровней на его входах из таблицы 6.3, определять состояние выхода Y логического элемента. Результаты занести в соответствующий столбец таблицы. Таблица 6.3

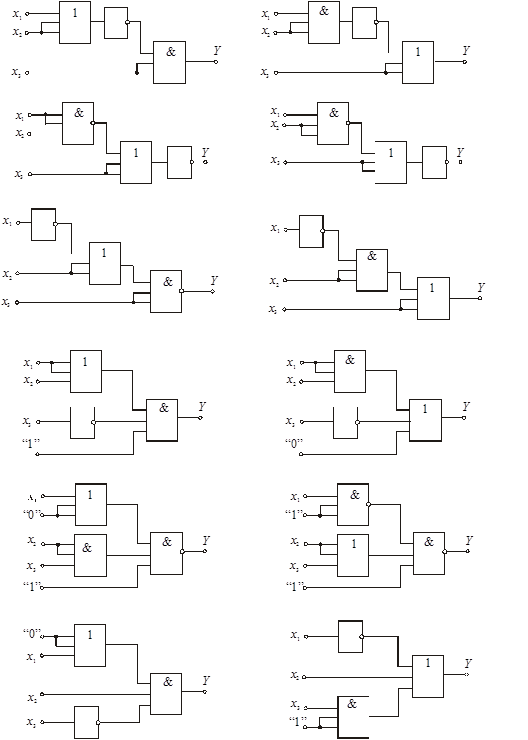

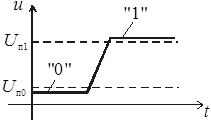

8 Определить уровень выходного сигнала элемента ИЛИ при свободных (неподключенных) входах. Результат занести в таблицу 6.2. 9 Повторить исследования согласно пп 7 и 8 для логических элементов И и И-НЕ. 10 Из имеющихся логических элементов собрать цифровое устройство, реализующее логическую функцию ИЛИ-НЕ. Экспериментально составить для него таблицу истинности по методике из п 7. 11 В соответствии с индивидуальным заданием собрать цифровое устройство в соответствии с одной из схем на рисунке 6.3. Определить и зафиксировать состояние выхода устройства Y при заданном сочетании уровней входных сигналов X1 X2 X3. Обработка экспериментальных данных 1. По результатам пп 3 и 4 сравнить напряжения, соответствующие уровням логических «0» и «1», на выходе логического элемента с напряжением питания ИМС. Сделать вывод об их соответствии уровням ТТЛ логики. 2. Проанализировать данные таблицы 6.2, полученные при неподключенных входах логических элементов. Объяснить полученные результаты с учетом напряжения на свободном входе Uвх, полученном в п 6. 3. Проанализировать экспериментальные данные, соответствующие таблицам истинности 6.1 и 6.3, и сделать вывод об их соответствии логике функционирования данных элементов и основным положениям булевой алгебры. 4. Индивидуально для заданной преподавателем схемы на рисунке 6.3 составить логическую функцию и таблицу истинности. Сравнить результаты для указанного сочетания уровней входных сигналов x1 x2 x3, полученные теоретически и экспериментально. Методические указания Импульсный режим работы и цифровое представление информации.Устройства, в которых происходит формирование или преобразование импульсных сигналов, называют импульсными. Класс импульсных устройств весьма широк, но в настоящее время большую часть их составляют цифровые логические устройства, которые являются базовыми для вычислительной техники и дискретной автоматики. В них осуществляется цифровое представление информации, характерное полным абстрагированием от особенностей электрических процессов в электронной схеме, выполняющей обработку сигналов. В цифровых устройствах чаще всего приходится иметь дело с прямоугольными импульсами или перепадами напряжения, изменяющимися между двумя условными уровнями: низким - уровнем логического нуля («0») и высоким - уровнем логической единицы («1»). Эти уровни в общем случае не связаны с конкретным значением напряжения. Они представляют собой информационные уровни, при этом, когда мгновенные значения сигнала u(t) превышают некоторый верхний пороговый уровень Uп1, они считаются соответствующими логической «1» (рисунок 6.4), а если значения сигнала становятся меньше нижнего порогового уровня Uп0, их относят к соответствующим логическому «0».

Рисунок 6.3

Рисунок 6.4 Сигнал, имеющий два информационных уровня («1» и «0») называется цифровым. Сигналы, не являющиеся цифровыми, называются аналоговыми. Классификация цифровых устройств.В общем случае устройства, оперирующие с цифровой (дискретной двоичной) информацией, подразделяются на два больших класса: комбинационные схемы (цифровые автоматы без памяти) и последовательностные устройства (цифровые автоматы с памятью). Память – это свойство системы сохранять в течении требуемого времени значения сигналов, характеризующих внутреннее состояние цифрового устройства. Все комбинационные схемы (их еще называют логическим устройствами) характеризуются отсутствием памяти. Сигналы на выходах комбинационной схемы в любой момент времени однозначно определяются сочетанием сигналов на его входах и не зависят от предыдущих состояний такого цифрового устройства. Их схемным признаком является отсутствие цепей обратной связи, т.е. замкнутых петель для прохождения сигналов с выхода на входы. К комбинационным схемам относят логические элементы, шифраторы и дешифраторы, мультиплексоры и демультиплексоры, большинство арифметических устройств. Последовательностные устройства обязательно содержат элементы памяти, и при смене информации на входах для предсказания сигналов на выходах таких устройств в данный момент времени необходимо знать также и состояние элементов памяти в предыдущий момент времени. Таким образом, реакция последовательностного устройства на определенные входные сигналы зависит от предыстории его работы. Последовательностные устройства организуются из комбинационных путем соответствующего их включения. Схемным признаком принадлежности устройства к последовательностному типу является наличие в нем обратных связей. К этому классу относятся триггеры, счетчики, регистры, запоминающие устройства. Параметры ИМС.Цифровые устройства в интегральном исполнении выпускаются в составе серий микросхем. Серия – это совокупность микросхем, характеризуемых общими технологическими и схемотехническими решениями, а также уровнями электрических сигналов и напряжений питания. При этом свойства каждого типа цифровой ИМС оцениваются рядом параметров, обусловленных внутренней структурой и внешним исполнением, причем ряд из этих параметров специфичен для данного типа ИМС, а другие характеризуют все изделия данной серии. Если в процессе эксплуатации эти параметры будут выдержаны, то фирма – изготовитель гарантирует нормальную работу. Сравнительную оценку ИМС осуществляют по следующим основным параметрам: быстродействию, напряжению питания, потребляемой мощности, коэффициенту разветвления по выходу, коэффициенту объединения по входу, помехоустойчивости, степени интеграции, надежности, устойчивости при климатических и механических воздействиях. Быстродействие характеризует максимальную частоту смены входных сигналов, при которой еще не нарушается нормальное функционирование устройства. Это один из важнейших параметров, так как он определяет время обработки информации. Быстродействие ИМС ограничено инерционностью полупроводниковых элементов и различного рода паразитными емкостями. Быстродействие ИМС, как правило, оценивается средним временем задержки распространению сигнала По быстродействию цифровые ИМС делятся на сверхбыстродействующие ( Коэффициент разветвления по выходу краз характеризует нагрузочную способность ИМС. Он определяет максимальное число входов элементов этой же серии, которые могут быть подключены к выходу данного цифрового устройства без нарушения его работоспособности. Значения краз могут варьировать от единиц до нескольких десятков. Коэффициент объединения по входу коб определяет число логических входов, которое имеет ИМС. Чаще всего коб Помехоустойчивость характеризует допустимый уровень напряжения помех на входах ИМС. В справочной литературе приводятся значения статической помехоустойчивости Степень интеграции элементов ИМС характеризует достигнутый при производстве технологический уровень. Численное значение степени интеграции определяется округленным до большего целого числа значением десятичного логарифма числа элементов в одном кристалле. Однако, поскольку на практике чаще важна степень интеграции не элементов, а логических функций, то все цифровые ИМС подразделяют по этому показателю следующим образом: - малой интеграции (несколько логических элементов или один – два триггера в корпусе); - средней степени интеграции (сложная логическая цепь или относительно простое функциональное устройство на одном кристалле); - большой интеграции (БИС) (в одном корпусе арифметическое устройство, многоразрядный счетчик и т.п.); - сверхбольшой степени интеграции (СБИС) (микропроцессоры, однокристальные ЭВМ и т.д.). Надежность ИМС определяется в значительной мере отказами соединений между контактными площадками на кристалле и выводами корпуса, а для БИС и СБИС определяющими могут оказаться отказы элементов и соединений внутри самого кристалла. Надежность характеризуется интенсивностью отказов, определяемой в ходе испытаний

где n - число отказов в ходе испытаний; t - время испытаний; N - число испытуемых изделий в партии. Для современных ИМС интенсивность отказов, как правило, составляет Устойчивость к механическим и климатическим воздействиям характеризует возможность применения ИМС при изменении температуры, влажности, радиации, воздействии ударов, вибрации, центробежной силы. В значительной степени она определяется типом используемого корпуса. Так, температурный диапазон выпускаемых серийно отечественных ИМС составляет от –10° до +70° С (общепромышленного, широкого применения в пластмассовом корпусе) и от –60° до +125° С (специального, применения, «военная приемка» в металлокерамическом корпусе обычно с позолоченными контактами). Условные графические обозначения цифровых ИМС.На принципиальных электрических схемах цифровые ИМС изображаются согласно ГОСТ 2.743-82 прямоугольниками со сторонами, кратными 5мм. При этом прямоугольник может содержать как основное поле, в верхней части которого указывают символ функции, так и два дополнительных, слева и справа от основного, с такой же кратностью сторон. Примеры изображения приведены на рисунке 6.5.

Рисунок 6.5 Входы показывают с левой стороны прямоугольника, выходы с правой, хотя допускается другая ориентация, когда входы располагают сверху, а выходы снизу. Выводы питания и общий обычно не показываются. При необходимости входы и выходы одинакового функционального назначения отделяются в дополнительных полях от других горизонтальными чертами, они могут иметь мнемонические обозначения. Причем, если расстояние между выводами одной группы равно с (кратное 5мм), то между соседними выводами, относящимися к различным группам, оно должно быть не менее l Свойства входов и выходов ИМС обозначают указателями. Прямые статические указателей не имеют. Инверсные статические входы и выходы помечают указателями логического отрицания - небольшим кружком у вывода как показано на рисунке 6.6,а. Динамические входы имеют несколько способов обозначения, как для управляющихся передним фронтом (прямой - рисунок 6.6,б), так и реагирующих на задний фронт (срез) импульса (инверсный - рисунок 6.6,в). Причем во всех трех случаях форма 1 рекомендуется как предпочтительная.

а б в Рисунок 6.6 Сравнительный анализ ТТЛ и КМОП цифровых ИМС.В зависимости от того, какие электронные приборы являются основными в ИМС, а также с учетом особенностей использованных схемотехнических решений, выделяют ряд классов цифровых ИМС (так называемых логик). Среди ИМС малой и средней степени интеграции наиболее широкое практическое применение в электронной аппаратуре различного назначения, в том числе и автомобильной, нашли два типа логики: транзисторно-транзисторная (ТТЛ) и ее модификации, а также логика на основе комплементарных (взаимодополняющих) ключей на МДП-транзисторах (КМДП, КМОП). На их основе можно в принципе построить любое цифровое устройство с требуемыми функциональными возможностями. Исключение составляют схемы БИС и СБИС, в которых преобладают логики на основе МОП транзисторов с каналами n–(n–МОП) и p-типа (p–МОП), и сверхбыстродействующая логика, в которой до недавнего времени господствующее положение занимала эмиттерно-связанная (ЭСЛ), а сейчас с ней начинает конкурировать логика на основе полупроводника арсенида галлия (GaAs). Такие ИМС могут работать при частотах сигнала 10 ГГц и выше. Основной особенностью ИМС ТТЛ является применение во входных цепях специфического электронного прибора – многоэмиттерного биполярного транзистора, отличающегося от обычных тем, что имеет несколько эмиттеров (2,3,4 или 8), объединенных общей базой. За рубежом ИМС данного типа имеют общее обозначение 54…/74…, причем цифры 54 соответствуют микросхемам специального назначения, а 74 предназначены для промышленной и коммерческой аппаратуры. Начало широкого применения ИМС ТТЛ относится к середине 60-х годов, когда были выпущены три базовых варианта данной логики: а) скоростная серия 54/74Н (отечественный аналог К131), б) стандартная – просто 54/74(К133/К155), в) микромощная серия 54/74L(К134 и бескорпусная серия 734). Растущие требования к повышению быстродействия и снижению потребляемой мощности привели к появлению новой разновидности ИМС ТТЛ с транзисторами Шоттки (ТТЛШ), в которых переход база – коллектор биполярных транзисторов шунтируется введением в схему металло – полупроводниковых выпрямляющих контактов (диодов с барьерами Шоттки), в результате чего уменьшается время их переключения за счет предотвращения насыщения транзисторов, а следовательно, и накопления носителей зарядов в области их баз. Наиболее популярной является так называемая «маломощная» серия ИМС 54/74LS (отечественные аналоги К533 и К555), которая стала универсальной в разновидности ТТЛШ. К началу 80-х годов она практически полностью вытеснила стандартную (К155). Затем появились усовершенствованные модификации ТТЛШ: быстродействующая 54/74AS (отечественные аналоги отсутствуют), микромощная серия 54/74ALS (К1533) и занимающая промежуточное положение 54/74F (К1531). Основные электрические параметры для всех серий ИМС ТТЛ одинаковы, за счет чего обеспечивается их полная совместность между собой, т.е. изделия, относящиеся к разным сериям, могут непосредственно соединяться друг с другом. Типовые значения этих параметров приведены в таблице 6.4, причем в скобках указаны напряжения питания ИМС специального назначения. Это позволяет при построении отдельных узлов сложных цифровых устройств использовать ИМС различных серий, наилучшим образом удовлетворяющих предъявляемым к ним функциональным и техническим требованиям. Там, где требуется высокое быстродействие, целесообразно применять серии К531 или К1531, если требуется малый расход энергии и устраивает пониженное быстродействие, наилучшим вариантом будут серии К134 и К1533. Разумный компромисс же обеспечивает серия К555. Таблица 6.4

Логические схемы на комплементарных (взаимодополняющих) МДП – транзисторах основаны на использовании последовательно включенных и управляемых одним сигналом МОП – транзисторов с каналами противоположных (р- и n- ) типов проводимости. Такая структура определяет основные достоинства ИМС КМОП: в статическом режиме они практически не потребляют мощности, имеют очень большое входное и малое выходное сопротивление. Первая серия таких микросхем 4000A (отечественный аналог К176) появилась в начале 1970–х. Наряду с достоинствами - потребление мощности зависит от скорости счета (в отличие от ТТЛ, у которых и в статическом, и в динамическом режиме потребление тока достаточно велико и различается мало), меньшая себестоимость, широкий диапазон напряжения питания – у нее оказались и существенные недостатки: чересчур большое время задержки переключения (порядка 100нс), разное выходное сопротивление в состояниях логических «0» и «1», недостаточный для специального применения температурный диапазон. Поэтому вскоре была выпущена модификация – так называемая «высоковольтная» серия 4000В (отечественные аналоги К561 и специального назначения К564), ИМС которой работают в диапазоне напряжения питания от 3 до 18В. Несмотря на то, что время задержки оказалось примерно в два раза большим, именно эта серия стала наиболее распространенной на практике, являясь по сути универсальной среди семейства КМОП логики, поскольку оказалась очень удобной не только для построения чисто цифровых узлов, но и в других областях импульсной техники. Следующий вариант данной разновидности – серия 4000UВ (К1561) – имеет быстродействие на уровне ИМС К176 при диапазоне напряжений питания и потребляемой мощности, как у серии К561. Основные электрические параметры ИМС К561 (К564) приведены в таблице 6.5.

Таблица 6.5

Отличительной особенностью разновидности 4000 является разная цоколевка по сравнению с ТТЛ при том, что функционально составы серий сходны между собой, поэтому непосредственная взаимная замена ИМС невозможна. Этот относительный недостаток был устранен в новой разновидности КМОП – логики, появившейся в начале 80-х годов, отличительной особенностью которой является внедрение технологии не металлических, а поликремневых затворов. Первой совместимой с ТТЛ серией, (причем и по обозначению) оказалась 54/74С (отечественный аналог отсутствует), которая способна работать и при «высоковольтном» напряжении питания 15 В. В дальнейшем эта технология позволила выпустить ИМС серий 54/74НС и 54/74НСТ (отечественный аналог К1564). Эти серии «низковольтные» (диапазон напряжения питания составляет от 2 до 6 В), но быстродействие их оказалось соизмеримым с универсальной серией К555 ТТЛШ, что позволило практически вытеснить ее из разрабатываемой электронной аппаратуры, а при необходимости и использовать совместно. Хотя ИМС К1564 имеют чуть более низкое быстродействие, но они оказались технологичнее в производстве. Последним достижением в совершенствовании ИМС КМОП являются серии 54/74АС (К1554) и 54/74АСТ (К1594), причем первая из них уступает по быстродействию только ИМС ТТЛШ К531 и К1531, а вторая оказалась более технологична, хотя и с меньшим быстродействием. Сравнительный анализ параметров ИМС различных серий ТТЛ и КМОП удобно производить для простейших устройств - логических элементов, набор которых одинаков во всех из этих серий, с помощью таблицы 6.6

Таблица 6.6

При применении ИМС КМОП удается снизить требования к стабильности напряжения источника питания ИМС КМОП обладают значительно лучшей помехоустойчивостью. Так, если допустимый уровень напряжения статической помехи ТТЛ нормируется в пределах 0,3В Это достоинство указывает на целесообразность применения именно ИМС КМОП в системах, имеющих длинные линии связи, а также при скрученном монтаже в условиях значительных перекрестных наводок. За счет высокого входного сопротивления ИМС КМОП в статическом режиме практически не нагружают выходов предыдущих каскадов. Поэтому нагрузочная способность их оказывается, как правило, значительно выше, чем у микросхем ТТЛ, коэффициент разветвления которых обычно не превышает 10. Однако следует иметь ввиду, что в динамическом режиме паразитные емкости входов ИМС КМОП затягивают переходные процессы в схеме, что приводит к увеличению токов, потребляемых от предыдущего каскада, а это, в свою очередь, обусловливает как снижение нагрузочной способности, так и увеличение потребляемой мощности, причем на высоких частотах она оказывается соизмеримой с микросхемами ТТЛШ. К достоинствам ИМС КМОП следует отнести также более предсказуемые уровни сигналов на их выходах (практически совпадающие с уровнями источника питания), что позволяет в целом ряде случаев точнее производить расчет функциональных устройств на их основе, и более высокую температурную стабильность параметров. Таким образом, несмотря на то, что ИМС ТТЛ до сих пор являются самыми распространенными, наиболее перспективной для применения в автомобильной электронной аппаратуре является КМОП логика. Причем, исходя из условий эксплуатации (широкий температурный диапазон) и напряжения питания бортовой сети целесообразно, если это позволяют требования по быстродействию цифровых устройств, использовать ИМС КМОП серии К564, в противном случае - серии К1554, К1564, К1594 (или их зарубежные аналоги) в специальном исполнении. При применении ИМС серий К561 (К564) следует учитывать существенную зависимость их быстродействия от напряжения питания и емкости нагрузки, что иллюстрируется таблицей 6.7. Таблица 6.7

Особенности применения ИМС. Специфика схемотехнических и технологических решений, использованных при производстве ИМС, накладывает определенные особенности на их «поведение» при монтаже, отладке и в процессе работы цифровых устройств. Так, при использовании ИМС наборов из нескольких простейших логических элементов часто оказывается, что отдельные из них остаются свободными. В этом случае рекомендуется данные элементы включать так, чтобы их выходы имели высокий потенциал («1»). В этом случае потребляемая ИМС мощность оказывается минимальной, а эти выходы можно использовать для создания логической «1» на входах других схем. С неиспользуемыми входами других ИМС ТТЛ поступают следующим образом: 1) объединяют с используемым, если это не нарушает принцип функционирования устройства и не ведет к превышению нагрузочной способности предыдущего каскада; 2) соединяют с общей шиной питания («землей»), когда на неиспользуемом входе должен быть уровень логического «0». 3) создают напряжение в пределах 2,4-3,6 В, если требуется уровень логической «1». Предупреждение. Нельзя подключать входы ИМС ТТЛ непосредственно к шине питания Uп, поскольку из-за большого входного тока в режиме логической «1» это может привести к пробою в схеме. Поэтому логическую «1» на входах ТТЛ обеспечивают одним из следующих способов: а) подключают к выходу свободного элемента, как было сказано выше в данном параграфе, с учетом его нагрузочной способности; б) неиспользуемые входы подсоединяют к источнику питания Uп через ограничивающий резистор с сопротивлением R0=1-2 КОм, как показано на рисунке 6.7. К этому резистору допускается присоединять до 20 входов ИМС ТТЛ;

Рисунок 6.7

в) в крайнем случае, можно оставить свободными, но этот способ уменьшает быстродействие и помехоустойчивость, особенно при большой частоте переключений, так как свободные входы подвержены влиянию наводок. Еще одна особенность ИМС ТТЛ связана с генерацией токов помех при переключениях. Амплитуда возникающих при этом импульсов напряжения на шинах питания и «земли» может оказаться достаточной для паразитного запуска соседних логических схем. Эта проблема решается, во-первых, установкой высокочастотных блокировочных конденсаторов ёмкостью Сб = 0,05-0,1мкФ между этими шинами непосредственно вблизи корпуса ИМС, а во-вторых, выполнением общей шины в виде широкой плоской полосы на печатной плате, чтобы уменьшить ее сопротивление и индуктивность. ИМС КМОП в принципе являются более критичными к условиям их применения, чем ТТЛ. Прежде всего, они чувствительны к статическим электрическим зарядам и наводкам от внешних источников. Очень большое входное сопротивление приводит к тому, что малейшая емкостная связь с внешним источником электрического поля создаст на разомкнутых затворах МОП - транзисторов потенциал в сотни вольт, и даже наличие на входах микросхем специальных защитных диодных структур не всегда помогает избежать их пробоя. Поэтому в процессе транспортировки и хранения выводы ИМС соединяют между собой обертыванием металлической фольгой, при монтаже целесообразно заземлять и низковольтный паяльник, и инструмент, и монтажный стол, а также не размыкать выводы до их присоединения к внешним, соединенным с общей шиной цепям. Кроме того, нельзя подводить электрические сигналы, в том числе напряжение питания к корпусу и холостым (неиспользуемым в функционировании ИМС) выводам. В отличие от ТТЛ входы ИМС КМОП оставлять свободными ни в коем случае нельзя, поскольку из-за наводок и связей через паразитные емкости на них могут возникнуть непредсказуемые напряжения, что может привести не только к неверному функционированию, но и выходу микросхемы из строя. Поэтому свободные входы в зависимости от их логических свойств следует соединять или с другими, задействованными, или, с одной из шин питания, правда, в отличие от ТТЛ при задании логической «1» (подключении к источнику Uп) ограничивающий резистор не требуется. Монтаж схем с ИМС КМОП следует производить внимательно, поскольку при случайных соединениях выхода с шинами питания через открытый транзистор протекает ток, ограниченный только сопротивлением канала и внутренним сопротивлением источника питания. Этот ток может вызвать тепловой пробой. Почти такой же эффект возникает в моменты переключений, если емкостная составляющая нагрузки ИМС превышает 500пФ. Еще один неожиданный эффект может возникнуть при соединении выхода ИМС ТТЛ со входом КМОП. При высоком уровне сигнала через защитный диод напряжение логической «1» проходит на вывод питания ИМС КМОП, и она за счет очень малого потребления тока до поры, до времени исправно работает даже при отсутствии соединения этого вывода с шиной Uп. И последнее. Для подавления помех, возникающих в цепях питания, рядом с корпусами ИМС КМОП целесообразно размещать блокировочные конденсаторы так же и такие же, как и в случае ТТЛ. При выполнении перечисленных выше сравнительно простых правил обеспечивается практически одинаково высокая надежность работы ИМС и ТТЛ, и КМОП. Особенности выходных каскадов цифровых ИМС.Большинство цифровых ИМС имеет двухтактные выходные каскады: уровни логических «0» и «1» подаются на выходы устройства через открытый биполярный (ТТЛ) или МОП (КМОП) транзистор. Такая схема, называемая активной нагрузкой, обеспечивает низкое выходное сопротивление при обоих уровнях, имеет малое время переключения, обладает более высокой помехоустойчивостью и обеспечивает меньшую потребляемую мощность по сравнению с одиночным транзистором, который использует в качестве коллекторной или стоковой нагрузки пассивный резистор. Однако существует ряд применений ИМС, когда активный выход оказывается неудобным. Одно из них связано с работой цифровых устройств на общую шину в микропроцессорной системе. Дело в том, что центральный процессор, память, а также различные периферийные устройства должны иметь возможность передавать и принимать многоразрядные (например, 16-разрядные) слова, и было бы неудобно и нецелесообразно использовать для соединения каждой пары устройств индивидуальный многожильный кабель. Для решения этой проблемы и используется так называемая шина (или магистраль) данных, т.е. один многожильный кабель, общий для всех устройств. При этом в каждый момент времени передавать информацию по ней может всего лишь одно из них, остальные же должны или работать только на прием, или быть совсем отключены от данной шины. Осуществить это с помощью цифровых ИМС с активным выходом невозможно, поскольку в любой момент времени их выходные выводы будут иметь определенный электрический потенциал (соответствующий «0» или «1»), который нежелательным образом повлияет на информацию, передаваемую по магистрали. Поэтому разработана и выпускается категория ИМС с так называемым третьим (или высокоимпедансным, или Z-)состоянием. Это ни в коем случае не означает, что на их выходах могут присутствовать три уровня напряжений. Просто в третьем состоянии оба оконечных транзистора цифрового устройства (биполярные VT1 и VT2 в примере на рис. 6.8) запираются соответствующими сигналами управления Uу1 и Uу2, что равносильно отключению выхода Q от нагрузки RH.

Рисунок 6.8

Перевод в это состояние осуществляется по специальному входу ИМС сигналом, который является приоритетным по сравнению с имеющимися на обычных логических входах. При работе на общую шину может использоваться и другая разновидность ИМС, называемая «с открытым коллектором», хотя в этом случае быстродействие и помехоустойчивость оказываются ниже. Данное название является довольно условным, поскольку появилось во время «господства» ТТЛ (по отношению же к КМОП логике правильнее было бы говорить об открытом стоке, а иногда и об открытом истоке), и означает, что один из двух транзисторов, являющийся активной нагрузкой, в схеме выходного каскада отсутствует, а один из электродов второго (коллектор, эмиттер, сток, исток) соединен только с соответствующим внешним выводом ИМС. Такой вывод и называют открытым. Если открытым является коллектор транзистора n-p-n типа, эмиттер транзистора p-n-p типа, сток транзистора с каналом n- типа, исток транзистора с каналом p-типа, то вывод обозначается символом Такие ИМС обладают существенно большей нагрузочной способностью и применяются обычно для непосредственного управления внешними устройствами, например элементами индикации, реле и т.п., которые к тому же могут работать от других источников с положительными напряжениями и меньше, и больше напряжения питания самой ИМС. Так микросхема ТТЛ К155ЛА11 позволяет подводить к выходному транзистору напряжение до 30В, а К564ЛА10 обладает нагрузочной способностью до 120 мА, что для КМОП логики является значительной величиной. На рисунке 6.9 показан пример управления элементом 2И-НЕ (К155ЛА11)

Рисунок 6.9 ИМС с открытым коллектором легко вводить в линейный (усилительный) режим работы, что иногда оказывается важным при построении различного ряда генераторных устройств. Еще одно применение таких микросхем связано с выполнением логических операций, поскольку элементы, входящие в их состав, допускают параллельное подключение нескольких выходов к общей нагрузке. Объединение выходов называют монтажной (проводной) логикой. Она в ряде случаев позволяет уменьшить аппаратные затраты при разработке цифровых устройств. Основные положения алгебры логики. Анализ и синтез цифровых устройств (логических цепей) производится на основе математического аппарата алгебры логики, или булевой алгебры. Поэтому прежде чем переходить к изложению материала, посвященного логическим интегральным схемам, необходимо рассмотреть основные понятия и законы этой алгебры. Переменные здесь могут принимать только одно из двух значений: Логическое сложение (дизъюнкция) обозначается символом «+» или V Y=a+b+c+… или Y=aVbV…, (6.2), где a, b, c - логические переменные. Логическая сумма равна единице тогда, когда равно единице одно или несколько слагаемых: 0+0=0; 0+1=0; 1+1+1+…+1=1 Логическое умножение (конъюнкция) обозначается точкой или символом Λ, либо вообще в буквенных выражениях никак не обозначается Y=abc… или Y=aΛbΛcΛ… (6.3) Логическое произведение будет равно единице только в том случае, если все сомножители равны единице: 0·0=0 0·1+0 1·1=1 Логическое отрицание (инверсия) обозначается чертой над обозначением аргумента. Y= Результатом данной операции является изменение значения переменной а на противоположное. Таким образом, инверсия единицы равна нулю, инверсия нуля - единице, а двойная инверсия не изменяет значения переменной:

Основываясь на приведенных числовых равенствах, запишем следующие выражения, в которых переменная а может принимать значение а+0=а; а+1=1; а+а+…+а=а; а+ а·0=0; а·1=а; аа…а=а; а

Основные законы алгебры логики. Переместительный закон: a+b=b+a; ab=ba. (6.5) Сочетательный закон: (a+b)+c=c+(b+c); (ab)c=a(bc). (6.6) Распределительный закон: a(b+c)=ab+аc; a+bc=(a+b)(a+c). (6.7) Последнее равенство можно получить в результате следующих преобразований: а+bс=a(1+b+с)+bc=а+аb+ас+bс=(а+ b)(a + с). (6.8) Закон поглощения: a+ ab=а(1+b)=а; а (а+b)=a+ab=a. (6.9) Закон склеивания: ab+a Закон отрицания (правило Де-Моргана):

Закон отрицания справедлив для любого числа переменных. Логический элемент (логический вентиль) - это электронная схема, выполняющая некоторую простейшую - дизъюнкцию, конъюнкцию или инверсию – или близкую к простейшей логическую операцию. Имея в распоряжении набор логических элементов, соответствующих функционально полной системе, можно реализовать любую, сколь угодно сложную логическую функцию. Поскольку вся логическая функция есть комбинация простейших функций - дизъюнкции, конъюнкции и инверсии, то набор из элементов трех типов, реализующих соответственно функции И, ИЛИ, и НЕ, естественно, является функционально полным. Например, функцию а Функционально полные системы могут представлять собой набор элементов, реализующих логические операции, отличные от простейших, в том числе и элементов одного типа - или И-НЕ (Y=aÙbÙcÙ…), или ИЛИ-НЕ (Y=avbvcv…). Логический элемент может быть реализован в виде отдельной ИМС, хотя, как правило, она одержит сразу несколько логических элементов одного типа. На рисунке 6.10 приведены условные графические изображения наиболее часто используемых на практике логических элементов, а в таблице 6.8 - буквенные обозначения ИМС, в состав которых они входят.

Рисунок 6.10 Таблица 6.8

*Не все ИМС с аббревиатурой «ЛП» содержат именно данные элементы. Логические элементы выпускаются в составе всех серий ИМС малой и средней степени интеграции, в том числе ТТЛ и КМОП, причем их выходы могут быть и активной нагрузкой, и с открытым коллектором (ок) или стоком. Наиболее удобными в практическом применении, а потому и самыми популярными и широко распространенными оказались двухвходовые элементы И-НЕ, по 4 которых (4 Число входов может быть и больше: три (по три элемента в корпусе ИМС 3 Таблица 6.9

Логические элементы используются в электронике, во-первых, для выполнения простых преобразований логических сигналов, а, во-вторых, как составные части более сложных функциональных устройств. Синтез комбинационных цепей проводится обычно в такой последовательности. Вначале составляется таблица функционирования логической цепи - таблица истинности. Эта таблица показывает, чему равен выходной сигнал цепи при различных сочетаниях входных сигналов. Затем исходя из таблицы истинности записывается логическая функция (при наличии некоторого опыта логическую функцию довольно часто удается написать сразу, минуя этап составления таблицы функционирования). После этого логическая функция минимизируется и преобразуется к виду, удобному для реализации на логических элементах заданного типа. Рассмотрим более подробно процесс синтеза комбинационных цепей на примере. Пусть необходимо построить мажоритарную ячейку (ячейку голосования) на три входа, т. е. такую ячейку, у которой сигнал на выходе равен единице тогда, когда большинство входных сигналов равно единице. Другими словами, сигнал на выходе ячейки должен быть равен единице, когда на двух или трех входах цепи присутствует сигнал единицы, в противном случае выходной сигнал должен быть равен нулю. Заполняем вначале таблицу истинности (таблица 6.10). Поскольку в данном случае имеются три входных сигнала х1, х2, х3, каждый из которых может принимать одно из двух возможных значений (0 или 1), то всего может быть восемь различных комбинаций этих сигналов. Четырем из этих комбинаций будет соответствовать выходной сигнал Y, равный единице. Пользуясь таблицей 6.10 можно написать логическую функцию, которую должна реализовать синтезируема цепь. Для этого нужно представить эту функцию в виде суммы логических произведений, соответст- Таблица 6.10

вующих тем строкам таблицы 6.10, для которых функция Y равна единице. При записи этих логических произведений следует брать соответствующий аргумент с инверсией или без нее в зависимости от того, чему равен этот аргумент в данной строке таблицы истинности, нулю или единице. В данном случае получим

Y=

В выражении (6.12) логическое произведение Для минимизации (упрощения) функции (6.12) можно применить основные законы алгебры логики. Возможна, например, следующая последовательность преобразований: F= +(х1х2 Как видим, полученное конечное выражение явно проще исходного. Если воспользоваться для построения логической цепи НЕ–И, то имеет смысл далее преобразовать функцию к виду

Рисунок 6.11 Из последнего выражения видно, что для построения проектируемой ячейки в данном случае потребуется три двухвходовых и один трехвходовой элемент НЕ–И. Схема синтезированной логической цепи приведена на рисунке 6.11. В настоящей работе исследуется пять логических элементов, представленных на рисунке 6.1: а) НЕ (инвертор); б) ИЛИ (дизъюнктор); в) И (конъюнктор); г) И–НЕ. Для лучшего восприятия импульса логического действия ТТЛ, выражаемого логической функцией, ее обычно задают в виде таблицы состояния входных xj и выходных Yj переменных. Такую таблицу называют также переключательной таблицей или таблицей истинности. Логическую функцию НЕ реализуют элементы ИМС, содержащие ключ с одним входом и одним выходом. Выходной сигнал этих ИМС всегда противоположен входному (Y= Таблица 6.11.

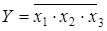

Реализация логической функции ИЛИ осуществляется логическими элементами - дизъюнкторами. Для трехходового элемента ИЛИ выходной сигнал будет соответствовать логической функции Y=x1+x2+x3, (6.13) и окажется равным «1», если хотя бы один из входных сигналов xi равен «1». Логическую функцию И реализуют элементы - конъюнкторы. Для трехвходового элемента И выходной сигнал будет определяться логическим умножением Y=x1 ×x2 ×x3. (6.14)

У этих элементов сигнал «1» появляется на выходе тогда и только тогда, когда на все входы одновременно поданы сигналы логической «1». В противном случае (даже при наличии на входе одного «0») выходной сигнал отсутствует (равен логическому «0»). Сигнал на выходе логического элемента И-НЕ, определяемый логическим выражением

является инверсным по сравнению с обычным элементом И. То есть, на его выходе появится уровень «0» только в том случае, если на всех входах действуют сигналы «1». Используя логические ИМС НЕ, ИЛИ, И, можно реализовать логическую функцию любой сложности, т.е. создать более сложное в функциональном отношении цифровое устройство. Примеры таких устройств приведены на рисунке 6.3.

Поиск по сайту: |

, равным среднему арифметическому задержек включения

, равным среднему арифметическому задержек включения  и выключения

и выключения  типового логического элемента серии (обычно инвертора).

типового логического элемента серии (обычно инвертора). нс), быстродействующие(5-10нс), среднего быстродействия(10-100нс), низкого быстродействия (

нс), быстродействующие(5-10нс), среднего быстродействия(10-100нс), низкого быстродействия (  8, что отчасти определяется ограниченным числом выводов. Однако всегда возможна реализация многовходовых комбинационных схем путем соединения отдельных ИМС с учетом законов булевой алгебры.

8, что отчасти определяется ограниченным числом выводов. Однако всегда возможна реализация многовходовых комбинационных схем путем соединения отдельных ИМС с учетом законов булевой алгебры. , представляющие максимально допустимое напряжение статической помехи (длительность которой больше времени переходных процессов в схеме) на входе, при котором ещё не происходит изменение выходных уровней цифрового устройства. Обычно значения

, представляющие максимально допустимое напряжение статической помехи (длительность которой больше времени переходных процессов в схеме) на входе, при котором ещё не происходит изменение выходных уровней цифрового устройства. Обычно значения  , (6.1)

, (6.1) =

=  , что соответствует вероятности безотказной работы

, что соответствует вероятности безотказной работы  %. Это очень высокий показатель.

%. Это очень высокий показатель.

2с.

2с.

, В

, В

, мА

(один ЛЭ)

, мА

(один ЛЭ)

, мА

, мА

нс

нс

, поскольку они допускают более широкий его диапазон изменения. Кроме того, за счет существенно меньшего потребляемого тока

, поскольку они допускают более широкий его диапазон изменения. Кроме того, за счет существенно меньшего потребляемого тока  1В, то у КМОП он составляет

1В, то у КМОП он составляет  и, как правило, находится на уровне 0,5 Uп.

и, как правило, находится на уровне 0,5 Uп. =5 В

=5 В

Выходы с тремя состояниями имеются у ИМС различного функционального назначения от простейших логических элементов до самых сложных БИС и СБИС, и обозначаются в схемах символом

Выходы с тремя состояниями имеются у ИМС различного функционального назначения от простейших логических элементов до самых сложных БИС и СБИС, и обозначаются в схемах символом  .

. . И, наоборот, при открытом коллекторе транзистора p-n-p ,эмиттере транзистора n-p-n, стоке транзистора с p-каналом, исток транзистора с n-каналом, вывод обозначают символом

. И, наоборот, при открытом коллекторе транзистора p-n-p ,эмиттере транзистора n-p-n, стоке транзистора с p-каналом, исток транзистора с n-каналом, вывод обозначают символом  .

.

(6.4)

(6.4)

=а.

=а. =a; (a+b) (a+

=a; (a+b) (a+  ;

;  . (6.11)

. (6.11)

2И-НЕ) входят в состав одной микросхемы.

2И-НЕ) входят в состав одной микросхемы. х2х3+х1

х2х3+х1  х3+х1х2

х3+х1х2  +х1х2х3 . (6.12)

+х1х2х3 . (6.12)

). При отсутствии на входе x сигнала, т.е. при логическом «0», на выходе Y будет высокий уровень напряжения, т.е. логическая «1», и наоборот. На рисунке 3.2. логический символ 0 указывает на инверсный выход. Для схемы НЕ таблица истинности имеет простой вид (таблица 6.11).

). При отсутствии на входе x сигнала, т.е. при логическом «0», на выходе Y будет высокий уровень напряжения, т.е. логическая «1», и наоборот. На рисунке 3.2. логический символ 0 указывает на инверсный выход. Для схемы НЕ таблица истинности имеет простой вид (таблица 6.11). , (6.15)

, (6.15)