|

|

|

Архитектура Астрономия Аудит Биология Ботаника Бухгалтерский учёт Войное дело Генетика География Геология Дизайн Искусство История Кино Кулинария Культура Литература Математика Медицина Металлургия Мифология Музыка Психология Религия Спорт Строительство Техника Транспорт Туризм Усадьба Физика Фотография Химия Экология Электричество Электроника Энергетика |

Счетчики с параллельным переносом ⇐ ПредыдущаяСтр 3 из 3

У них счетные импульсы подаются одновременно на все тактовые входы, а каждый из триггеров цепочки служит по отношению к последующему только источником информационных сигналов. Срабатывание триггеров параллельного счетчика происходит синхронно, а задержка переключения всего счетчика равна задержке одно триггера.

В счетчике с параллельно-последовательным переносомтриггеры соединены в группы так, что отдельные группы образуют счетчики с параллельным переносом внутри группы, а группы соединяются в счетчик с последовательным переносом. Общий коэффициент счета равен произведению коэффициентов счета всех групп.

Счетчики ТТЛ с последовательным переносом Состоят из 4-х одинаковых JK-триггеров, которые могут использоваться как по прямому назначению, так и в качестве ТК-триггеров. Переброс осуществляется по срезу. Три триггера соединяются в последовательную цепочку, 4-й самостоятельно. ИЕ5

ИЕ4 (ИЕ5)

ИЕ4

Изменить коэффициент пересчета возможно с помощью R(S)-входов.

ИЕ2

При последовательном соединение (Q1 к С2) схема работает как 10-ый счетчик в коде 8-4-2-1, но на выходе не получается меандр. Если Т1 включен последним, счетчик работает в коде 5-4-2-1 и на выходе будет меандр.

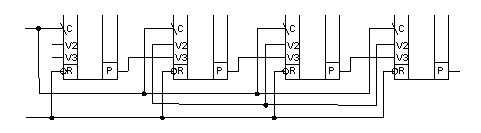

Счетчик ТТЛ с параллельным переносом Двоично-десятичный суммирующий счетчик. Имеет 4 входа предварительной установки счетчика при V1=0 независимо от предыдущего состояния и сигналов на входах С, V2, V3. При При «1» на входе V3 на выходе Р формируется импульс логической «1» (перенос) с девятым входным импульсом. V3 – разрешает перенос. V2=0 – прерывает счет, однако информация на выходах при этом сохраняется. V1 – предварительная запись.

Быстродействующий синхронный многокаскадный счетчик

Синхронный многокаскадный счётчик

ИЕ6, ИЕ7

4-х разрядные быстродействующие реверсивные счетчики-делители с параллельным переносом между разрядами. По входам предварительной информации D ввод производится при низком уровне на С. Входы +1 и -1 счетные. Последовательность входных импульсов подается на один из этих входов в зависимости от того, в каком направлении (прямом / обратном) требуется вести счет. На выходе ≥15 (≥9) появляется импульс при выходной комбинации «1111» («1001»). На выходе ≤0 – при «0000». Меньше нуля – для режима вычитания.

Наращивание счетчиков Последовательный.

Последовательный быстродействующий

ИЕ8

ИЕ14 (ИЕ15) Функциональные микросхемы аналогичны ИЕ2 и ИЕ5. Имеют входы предварительной установки D высоким уровнем на Е. 1. Фильтры Салена и Кея. Фильтр нижних частот 2. Фильтры Салена и Кея. Фильтр верхних частот 3. Полосовой фильтр с параллельной ОС 4. Универсальный фильтр с фиксированным усилением 5. Универсальный фильтр с регулируемым усилением (независимо от Q) 6. Биквадратный фильтр 7. Гиратор 8. Структурная схема импульсного блока питания 9. ПН Безтрансформаторный с независимым возбуждением. 10. Трансформаторный с самовозбуждением 11. Двухтактный ПН с самовозбуждением охваченный трансформаторной положительной ОС 12. Преобразователи с независимым возбуждением 13. Мостовая схема 14. Однотактный преобразователь с прямым включением диода (ОПНП) 15. Однотактный преобразователь с обратным включением диода (ОПНО) 16. Резонансные преобразователи 17. Тиристорные преобразователи 18. Элемент три «И-НЕ» на ДТЛ. 19. Базовый элемент ЭСЛ – эмиттерно-связанная логика. 20. Двунаправленный ключ. 21. Инвертор КМОП 22. Схема И-НЕ 23. Схема ИЛИ-НЕ 24. RS-триггер 25. Триггерные системы - RS-триггер как ячейка памяти и УУ. 26. Синхронные RS-триггеры. 27. Двухступенчатые RS-триггеры. 28. JK-триггеры 29. RS-триггер. ( в скобках R-триггер) 30. Е-триггер 31. D-триггеры 32. DV-триггеры 33. TV-триггер Сихронный TV-триггер 34. Несимметричные триггеры (Триггеры Шмита). 35. Счётчик ИЕ4 36. Счётчик ИЕ2 37. Быстродействующий синхронный многокаскадный счетчик 38. Синхронный многокаскадный 39. ИЕ6, ИЕ7 40. Наращивание счетчиков Последовательный. 41. Наращивание счётчиков. Последовательный быстродействующий 42. 4-х разрядный сдвигающий регистр с последовательным вводом. 43. Четырехразрядный регистр сдвига ИР-1 44. Универсальный 8-ми разрядный регистр сдвига ИР-13 45. 4-х разрядный регистр хранения ИР-15 46. Сумматор 47. Последовательный сумматор. 48. Сумматоры ТТЛ 49. ИМ2 – двухразрядный полный сумматор. ИМ3 – четырехразрядный полный сумматор. 50. Умножитель

Поиск по сайту: |

происходит нормальный счет, причем переброс осуществляется по переднему фронту. Счет либо от нуля, либо от информации, записанной на входы D.

происходит нормальный счет, причем переброс осуществляется по переднему фронту. Счет либо от нуля, либо от информации, записанной на входы D.