|

|

|

Архитектура Астрономия Аудит Биология Ботаника Бухгалтерский учёт Войное дело Генетика География Геология Дизайн Искусство История Кино Кулинария Культура Литература Математика Медицина Металлургия Мифология Музыка Психология Религия Спорт Строительство Техника Транспорт Туризм Усадьба Физика Фотография Химия Экология Электричество Электроника Энергетика |

АЦП последовательного счета

Самый простой АЦП – это компаратор, работа которого рассмотрена в главе 11 (рис. 11.10). Это одноразрядный АЦП, который имеет только одну ступень квантования. Подобные АЦП находили применение в гибридных ЭВМ. Более сложный АЦП имеет несколько ступеней квантования. Далее будут рассмотрены несколько вариантов построения АЦП. Структурная схема АЦП последовательного счета с предварительным преобразованием напряжения в частоту представлена на рис. 14.6.

Рис. 14.6. Структурная схема интегрирующего АЦП последовательного счета Двоичный счетчик подсчитывает число импульсов, поступивших от преобразователя напряжения в частоту (ПНЧ) за период Тсч, фиксируемый генератором импульсов заданной длительности (ГИЗД). По окончании счета код счетчика заносится в регистр, а перед началом нового счета счетчик сбрасывается в нулевое состояние по входу R. Преобразователи напряжения в частоту могут быть выполнены с применением различных элементов и схем. Одна из схем приведена на рис. 14.7. Входной сигнал Uвх интегрируется и подается на устройство сравнения, на другой вход которого поступает напряжение U0 от источника опорного напряжения ИОН. В момент равенства выходного напряжения интегратора Uи и напряжения U0 устройство сравнения включает формирователь импульсов обратной связи СФ (например, одновибратор), формирующий в течение интервала времени tос импульс амплитудой Uос, постоянной вольт-секундной площади Uос tос (рис. 14.7, б). Цикл работы формирователя определяется интервалом времени Тх = tинт + tос, зависящим от значения напряжения Uвх.

а б Рис. 14.7. Структурная схема (а) и временная диаграмма (б) преобразователя напряжения в частоту

При прямоугольной форме импульсов амплитудой Uос:

Uвх tинт / t1 = U0= Uос tос/ t2 – Uвх tос / t1; Uвх (tинт+ tос) / t1 = Uвх Тх /t1 = Uос tос/ t2,

где R1C = t1; R2C = t2; Тх = tинт + tос = 1 / fвых. Следовательно, уравнение преобразования можно записать в виде fвых = 1 / Тх = Uвх t2/t1 Uос tос = Uвх R2 / R1 Uос tос = k Uвх ,

т. е. параметры преобразователя не зависят от значений емкости С и образцового напряжения U0 и определяются только отношением сопротивлений интегратора и стабильностью площади импульса обратной связи. На значение общей погрешности преобразователя существенное значение может оказать дрейф нуля интегратора, поэтому в схемах преобразователей малых напряжений в частоту используют различные способы компенсации дрейфа нуля интегратора. Рассмотренный способ преобразования аналогового сигнала в код используется в микросхеме типа КР1108ПП1, которая преобразует положительные и отрицательные уровни входного напряжения ±10 В в импульсы прямоугольной формы с калиброванной длительностью, а также служит для преобразования частоты в напряжение (ПНЧ – ПЧН). В [3] приведена схема включения микросхемы в режиме ПНЧ для преобразования положительного напряжения 0…10 В в частоту от 0 Гц до 10 кГц. При этом крутизна преобразования равна 1 кГц/В (т. е. каждый выходной импульс соответствует приращению входного напряжения на 1 мВ). Более высокую точность имеет АЦП двойного интегрирования, схема которого приведена на рис. 14.8.

а б Рис. 14.8. АЦП с двойным интегрированием: а – структура; б – временная диаграмма

В двухтактном АЦП преобразование аналогового сигнала в код проходит две стадии: стадию интегрирования и стадию счета. В начале первой стадии ключ Кн1 замкнут, а ключ Кн2 разомкнут. В момент начала преобразования установленный управляющим устройством УУ на нуль по входу R счетчик запускается. С этого момента до момента tо формируется временной интервал t – время первичного интегрирования. В течение интервала t ключ Кн1 замкнут, а входное напряжение предполагается постоянным. Интегратор интегрирует входное напряжение. На выходе интегратора напряжение к моменту окончания интегрирования составляет

После окончания первой стадии интегрирования счетчик формирует сигнал окончания первого интервала Uк, ключ Кн1 размыкается, а ключ Кн2 замыкается и на вход интегратора поступает опорное напряжение от источника опорного напряжения ИОН. При этом опорное напряжение выбирается противоположным по знаку входному напряжению. На второй стадии, стадии счета, выходное напряжение интегратора линейно уменьшается по абсолютной величине, как показано на рис. 14.8. Счетчик подсчитывает число импульсов, пропорциональное длительности второго интервала интегрирования. Стадия счета заканчивается, когда выходное напряжение интегратора переходит через нуль. В момент такого пересечения срабатывает компаратор К, напряжение на выходе компаратора Uк становится равным нулю и по входу V счетчика прекращает подсчет импульсов. Отличительной особенностью метода двухтактного интегрирования является снижение влияния помех на результат преобразования вследствие того, что содержимое счетчика после окончания счета определяется усредненным значением входного напряжения за время t. Поэтому переменные составляющие входного напряжения в значительной степени ослабляются. Благодаря высокой точности преобразования двухтактные АЦП находят преимущественное применение в измерительной технике. В качестве примера преобразователей рассмотренного типа можно указать ИМС 11-разрядного АЦП К572ПВ2. К преобразователям последовательного счета относятся АЦП с единичным приближением (со ступенчатым пилообразным напряжением), основанные на уравновешивании входного аналогового сигнала суммой минимальных (для данного преобразователя) по весу квантов. Другое название такого преобразователя – АЦП с постоянными ступеньками. Схема такого преобразователя и временная диаграмма процесса преобразования приведены на рис. 14.9. Схема состоит из компаратора, счетчика и цифроаналогового преобразователя (ЦАП).

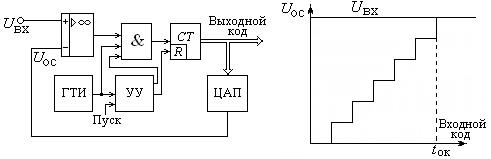

а б Рис. 14.9. АЦП последовательного счета с единичным приближением: а – структурная схема; б – временная диаграмма процесса преобразования

На один вход компаратора поступает преобразуемый сигнал Uвх, а на другой – сигнал обратной связи Uос с ЦАП. В исходном состоянии выход компаратора равен логической единице. С приходом импульса «Пуск» управляющее устройство УУ устанавливает счетчик в нулевое состояние и разрешает работу счетчика, который суммирует импульсы, поступающие с генератора тактовых импульсов ГТИ. Выходной код счетчика подается на ЦАП, осуществляющий преобразование этого кода в напряжение обратной связи Uос. Подсчет импульсов и линейно-ступенчатое возрастание напряжения обратной связи продолжается до тех пор, пока в некоторый момент времени tок напряжение обратной связи не сравняется с входным напряжением. В этот момент компаратор переключится в состояние логического нуля и запретит поступление тактовых импульсов на счетчик. Интервал от момента запуска АЦП до момента прекращения счета называется временем преобразования. Время преобразования последовательного АЦП является переменным и зависит от входного напряжения. Его максимальное значение соответствует максимальному входному напряжению. Быстродействие АЦП определяется числом разрядов п и частотой счетных импульсов fсч. При заданной разрядности АЦП время преобразования определяется частотой следования счетных импульсов. Максимальное время преобразования, соответствующее максимальному входному напряжению, tок = (2n – 1) Dtсч,

где Dtсч = 1 / fсч – период следования счетных импульсов.

Быстродействие АЦП существенно возрастает при организации следящего режима. Этот режим характерен тем, что компенсация входного сигнала в каждом последующем цикле преобразования начинается не с конечного (нулевого или максимального) значения, а со значения, установленного в предыдущем цикле, т. е. без переключения счетчика в исходное (нулевое) состояние. Подход к состоянию равновесия при следящем уравновешивании может осуществляться с двух сторон: как снизу, так и сверху. Непосредственно после включения, до достижения первого состояния равновесия, прибор следящего уравновешивания работает аналогично прибору последовательного счета с единичным приближением. Схема АЦП, работающего в следящем режиме, представлена на рис. 14.10. На сравнивающее устройство, как и в предыдущей схеме, подаются преобразуемое напряжение Uвх и компенсирующее Uос, полученное обратным преобразованием кода в напряжение с помощью ЦАП. Схема сравнения управляет двумя схемами совпадения И, на входы которых подаются импульсы от генератора тактовых импульсов ГТИ. Если Uвх > Uос, открывается схема совпадения, соединяющая генератор с суммирующим входом счетчика СТ. При Uвх < Uос открывается вычитающий вход счетчика и выходной код уменьшается. Как только компенсирующее напряжение Uос достигает преобразуемого, обе схемы совпадения закрываются. Код преобразуемого напряжения определяется состоянием счетчика.

Рис. 14.10. Блок-схема АЦП (а) и график следящего уравновешивания (б) Параллельный АЦП Простейший АЦП – компаратор – сравнивает входной сигнал с одним заданным значением. Такой АЦП является одноразрядным. Чтобы получить многоразрядный АЦП, нужно применить несколько компараторов и несколько заданных уровней, с которыми одновременно должен сравниваться входной сигнал. Число компараторов определяется числом разрядов выходного кода N = 2n – 1, где n – число разрядов. На рис. 14.11 показана реализация параллельного метода аналого-цифрового преобразования для трехразрядного числа. Структура параллельного АЦП состоит из 7 компараторов, преобразователя кода (шифратора), регистра и резисторной матрицы (РМ). Резисторная матрица создает из опорного напряжения Uоп 7 значений опорных напряжений, с которыми сравнивается преобразуемое напряжение Uвх. Общее сопротивление резисторной матрицы равно 7R. Поэтому на каждом из резисторов R создается падение напряжения, равное Uоп/7, на резисторах R/2 – Uоп/14. Значения опорных напряжений в относительных единицах приведены на рис. 14.5, а. Входное напряжение поступает на все компараторы одновременно, на другие входы компараторов подаются опорные напряжения.

Рис. 14.11. Схема трехразрядного параллельного АЦП

Если входное напряжение меньше половины ступени квантования h (Uвх < Uоп/14 = 0,5 h), то на выходах всех компараторов логический нуль. Если 0,5 h < Uвх <1,5 h, то компаратор 1 будет находиться в состоянии логической единицы, а остальные – в нулевом состоянии. На выходе АЦП в младшем разряде появится логическая единица. При Uвх > 1,5 h в единичном состоянии будут компараторы 1 и 2, и т. д. Состояния АЦП при различных уровнях входного сигнала (в условных единицах) представлены в табл. 14.1. Таблица 14.1

Из таблицы состояний следует что, при повышении Uвх от 0 до максимума компараторы устанавливаются в состояние 1 по очереди – от младшего к старшему. Если считывать показания АЦП непосредственно с выходов преобразователя, то при использовании двоичного кода возможно появление ошибок. Рассмотрим, например, переход от трех к четырем, или в двоичном коде от 0112 к 1002. Если старший разряд вследствие меньшего времени задержки в компараторе и шифраторе изменит свое состояние раньше двух других разрядов, то временно на выходе возникнет число 1112, т. е. семь. Так как результат аналого-цифрового преобразования, как правило, записывается в запоминающее устройство, возможна запись неверной информации. Решают эту проблему различными способами. Между компараторами и шифратором можно установить специальное логическое устройство, которое определяет высший номер сработавшего компаратора и вырабатывает соответствующий ему код. Приоритетное кодирование позволяет избежать ошибки, возможной из-за этого обстоятельства, поскольку единицы в младших разрядах не принимаются во внимание шифратором. Другой путь состоит в использовании кода Грея, что показано в табл. 14.1. Благодаря одновременной работе компараторов параллельные АЦП обладают самым высоким быстродействием среди других типов АЦП, определяемым быстродействием компараторов и задержками в кодирующем устройстве. Недостатком их является необходимость в большом количестве компараторов. Так, для восьмиразрядного АЦП требуется 255 компараторов. Следствием этого является высокая стоимость и значительная потребляемая мощность. К микросхемам этого типа относятся выпускаемые нашей промышленностью шестиразрядные АЦП К1107ПВ1 (Рпот = 1 вт), К1107ПВ3 (Рпот = 0,5 вт), восьмиразрядные К1107ПВ2 и К1107ПВ4 (Рпот = 3,5 вт) с частотой преобразования до 100 МГц. Для снижения аппаратурных затрат параллельных преобразователей применяют параллельно-последовательный метод построения АЦП. Параллельно-последовательные АЦП являются компромиссом между стремлением получить высокое быстродействие и желанием сделать это меньшей ценой. К последовательно-параллельным АЦП относятся многоступенчатые, конвейерные, многотактные АЦП [1, 3, 4].

Сигма-дельта АЦП АЦП параллельного интегрирования имеют ряд недостатков. Во-первых, нелинейность переходной статической характеристики операционного усилителя заметным образом сказывается на интегральной нелинейности характеристики преобразования АЦП высокого разрешения. Для уменьшения влияния этого фактора АЦП изготавливают многотактными. Другим недостатком этих АЦП является то обстоятельство, что интегрирование входного сигнала занимает в цикле преобразования только приблизительно третью часть. Две трети цикла преобразователь не принимает входной сигнал. Это ухудшает помехоподавляющие свойства интегрирующего АЦП. В-третьих, АЦП многотактного интегрирования должен быть снабжен довольно большим количеством внешних резисторов и конденсаторов с высококачественным диэлектриком, что значительно увеличивает место, занимаемое преобразователем на плате и, как следствие, усиливает влияние помех.

Рис. 14.12. Структурная схема сигма-дельта модулятора

Эти недостатки во многом устранены в конструкции сигма-дельта АЦП (в ранней литературе эти преобразователи назывались АЦП с уравновешиванием или балансом зарядов). Своим названием эти преобразователи обязаны наличием в них двух блоков: сумматора (обозначение операции – ∑) и интегратора (обозначение операции – ∆). Один из принципов, заложенных в таких преобразователях, позволяющий уменьшить погрешность, вносимую шумами, а, следовательно, увеличить разрешающую способность – это усреднение результатов измерения на большом интервале времени. Основные узлы АЦП – это сигма-дельта модулятор и цифровой фильтр. Схема n-разрядного сигма-дельта модулятора первого порядка приведена на рис. 14.12. Работа этой схемы основана на вычитании из входного сигнала Uвх(t) величины сигнала на выходе ЦАП, полученной на предыдущем такте работы схемы. Полученная разность интегрируется, а затем преобразуется в код параллельным АЦП невысокой разрядности. Последовательность кодов поступает на цифровой фильтр нижних частот. Порядок модулятора определяется численностью интеграторов и сумматоров в его схеме. Сигма-дельта модуляторы N-го порядка содержат N сумматоров и N интеграторов и обеспечивают большее соотношение сигнал/шум при той же частоте отсчетов, чем модуляторы первого порядка.

Рис. 14.13. Структурная схема сигма-дельта АЦП

Наиболее широко в составе ИМС используются однобитные сигма-дельта модуляторы, в которых в качестве АЦП используется компаратор, а в качестве ЦАП - аналоговый коммутатор (рис. 14.13). Принцип действия пояснен в табл. 2 на примере преобразования входного сигнала, равного 0,6 В, при Uоп=1 В. Пусть постоянная времени интегрирования интегратора численно равна периоду тактовых импульсов. В нулевом периоде выходное напряжение интегратора сбрасывается в нуль. На выходе ЦАП также устанавливается нулевое напряжение. Затем схема проходит через показанную в табл. 14.2 последовательность состояний.

Таблица 14.2

В тактовые периоды 2 и 7 состояния системы идентичны, так как при неизменном входном сигнале Uвх=0,6 В цикл работы занимает пять тактовых периодов. Усреднение выходного сигнала ЦАП за цикл действительно дает величину напряжения 0,6 В:

Для формирования выходного кода такого преобразователя необходимо каким-либо образом преобразовать последовательность бит на выходе компаратора в виде унитарного кода в последовательный или параллельный двоичный позиционный код. В простейшем случае это можно сделать с помощью двоичного счетчика. Возьмем в нашем примере 4-разрядный счетчик. Подсчет бит на выходе компаратора за 16-тактный цикл дает число 13. Несложно увидеть, что при Uвх =1 В на выходе компаратора всегда будет единица, что дает за цикл число 16, т.е. переполнение счетчика. Напротив, при Uвх =-1 В на выходе компаратора всегда будет нуль, что дает равное нулю содержимое счетчика в конце цикла. В случае, если Uвх =0 то, как это видно из табл. 14.2, результат счета за цикл составит 810 или 10002. Это значит, что выходное число АЦП представляется в смещенном коде. В рассмотренном примере верхняя граница полной шкалы составит 11112 или +710, а нижняя - 00002 или -810. При Uвх =0,6 В, как это видно из левой половины табл. 14.2, содержимое счетчика составит 1310 в смещенном коде, что соответствует +5. Учитывая, что +8 соответствует Uвх =1 В, найдем 5*1/8=0,625 > 0,6 В. При использовании двоичного счетчика в качестве преобразователя потока битов, поступающих с выхода компаратора, необходимо выделять фиксированный цикл преобразования, длительность которого равна произведению Ксчfтакт. После его окончания должно производиться считывание результата, например, с помощью регистра-защелки и обнуление счетчика. В этом случае с точки зрения помехоподавляющих свойств сигма-дельта АЦП близки к АЦП многотактного интегрирования. Более эффективно с этой точки зрения применение в сигма-дельта АЦП цифровых фильтров с конечной длительностью переходных процессов. Сравнение сигма-дельта АЦП с АЦП многотактного интегрирования показывает значительные преимущества первых. Прежде всего, линейность характеристики преобразования сигма-дельта АЦП выше, чем у АЦП многотактного интегрирования равной стоимости. Это объясняется тем, что интегратор сигма-дельта АЦП работает в значительно более узком динамическом диапазоне, и нелинейность переходной характеристики усилителя, на котором построен интегратор, сказывается значительно меньше. Емкость конденсатора интегратора у сигма-дельта АЦП значительно меньше (десятки пикофарад), так что этот конденсатор может быть изготовлен прямо на кристалле ИМС. Как следствие, сигма-дельта АЦП практически не имеет внешних элементов, что существенно сокращает площадь, занимаемую им на плате, и снижает уровень шумов. В результате, например, 24-разрядный сигма-дельта АЦП AD7714 изготавливается в виде однокристальной ИМС в 24-выводном корпусе и потребляет 3 мВт мощности, а 18-разрядный АЦП восьмитактного интегрирования HI-7159 потребляет 75 мВт. К тому же сигма-дельта АЦП начинает давать правильный результат через 3-4 отсчета после скачкообразного изменения входного сигнала, что при величине первой частоты режекции, равной 50 Гц, и 20-разрядном разрешении составляет 60-80 мс, а минимальное время преобразования АЦП HI-7159 для 18-разрядного разрешения и той же частоты режекции составляет 140 мс. В настоящее время ряд ведущих по аналого-цифровым ИМС фирм прекратили производство АЦП многотактного интегрирования, полностью перейдя в области АЦ-преобразования высокого разрешения на сигма-дельта АЦП. Сигма-дельта АЦП высокого разрешения имеют развитую цифровую часть, включающую микроконтроллер. Это позволяет реализовать режимы автоматической установки нуля и самокалибровки полной шкалы, хранить калибровочные коэффициенты и передавать их по запросу внешнего процессора.

ЗАКЛЮЧЕНИЕ

Сравнительно ограниченный объем учебного пособия не позволил рассмотреть все вопросы, возникающие при изучении схемотехники ЭВМ. Степень важности опущенных или кратко изложенных вопросов различна. Одни из них носят чисто познавательный характер (например, история развития схемотехники ЭВМ), другие – производственный (например, технология изготовления микросхем различных типов или функциональных блоков ЭВМ), третьи имеют сугубо теоретический аспект (например, влияние шума квантования в АЦП на величину погрешности преобразования). При необходимости углубленные сведения по затронутым вопросам можно найти в литературных источниках, приведенных в библиографическом списке [1–18]. Вопросы истории развития схемотехники ЭВМ более подробно изложены в [1, 4]. В нашем учебном пособии рассмотрены лишь основные варианты схемной реализации микросхем различных видов логик, а более подробные сведения приведены в [3 , 13]. Теоретические основы работы сложного инвертора базового элемента ТТЛ рассмотрены с целью пояснения принципа работы устройства. При необходимости информацию о влиянии отдельных элементов каскадной схемы инвертора на вид проходной характеристики можно найти в [1, 2]. Вопросы реализации комбинационных устройств (шифраторов, дешифраторов, преобразователей кодов, произвольных нестандартных функций) на основе программируемых логических матриц рассмотрены в учебном пособии сравнительно кратко. Более подробные сведения по этим вопросам можно почерпнуть в [1, 15]. В данном учебном пособии рассмотрены лишь основные типы цап и АЦП. Среди последовательных ЦАП, выпускаемых промышленностью и применяемых в различных устройствах, дополнительно можно рассмотреть ЦАП с широтно-импульсной модуляцией, на переключаемых конденсаторах. Не рассмотрены АЦП последовательного приближения (АЦП с поразрядным уравновешиванием), конвейерные АЦП. Сведения об этих устройствах приведены в [11, 16]. Схемотехника ЭВМ относится к научно-техническому направлению, которое быстро развивается. Это приводит к тому, что учебники и учебные пособия быстро устаревают. Отсюда большое значение приобретает знакомство студентов с периодической литературой. К таким источникам относятся, например, зарубежные журналы Electronic Design и Electronic Design News (имеется сетевой вариант) и отечественные журналы Электроника НТБ (наука, технология, бизнес), Электронные компоненты, Схемотехника, Компоненты и технологии.

Поиск по сайту: |

а б

а б