|

|

|

Архитектура Астрономия Аудит Биология Ботаника Бухгалтерский учёт Войное дело Генетика География Геология Дизайн Искусство История Кино Кулинария Культура Литература Математика Медицина Металлургия Мифология Музыка Психология Религия Спорт Строительство Техника Транспорт Туризм Усадьба Физика Фотография Химия Экология Электричество Электроника Энергетика |

Арх-ра процессора.Параллельн обработка инф. Конвейеризация

Архитектура-концепция, определяющая модель,структуру,выполн-е ф-ии и взаимосвязь компонентов сложного объекта . Арх мп отражает: структуру (регистровая модель),Способы представления и форматы данных,Способы обращения к программно доступным элементам, Набор операций, выполняемых МП (система команд),Характеристики управляющих слов и сигналов, вырабатываемых процессором и поступающих в МП, Реакция на внешние сигналы. Типы процессорной архитектуры: 1)CISC – Complex Instruction Set Computing (Архитектура полного набора команд)- использует набор машинных инструкций, полностью соответствующих набору команд ассемблера. Вычисления разного типа выполняются разыми инструкциями даже если приводят к одному результату.Достоинство архитектуры: обеспечивает разнообразные способы выполнения вычисляемых операции на уровне машинных команд.Недостатки архитектуры: Для каждой инструкции требуется большое количество тактов процессора. 2)Архитектура RISC: Reduced Instruction Set Computing Процессор использует набор наиболее употребляемых инструкций, который определяет в результате статистического анализа большого числа программ для основных областей применения CISC процессоров.Сложные инструкции отсутствуют. RICS-процессор оптимизирует каждую команду для быстрого выполнения. 2 основные тенденции: - Super pipelining(суперконвеерная обработка) - способ предварительной обработки при которой выполняется более чем 1 инструкция.Каждая фаза через которую проходит RISC команда (выборка – декодирование, выполнение, сохранение) занимает 1 такт.Сложные RISC-команды реализуются программно, а не аппаратно. - Super Scalar(суперскалярность) -В одном мп организуется несколько независимых программных каналов, встроенный планировщик просматривает вперед очередь команд, определяет группы, которые не будут конфликтовать друг с другом и пропускает группы на выполнение. В наст врем RISC-архитектура внедряется в архитектуру CISC по следующим направлениям: суперкомпьютеры с массовой параллельной обработкой; серверы;PC; Встраиваемые устройства управления периферийным оборудованием; Специализируемые встраиваемые устройства управления. Достоинства: · Более эффективная работа процессора на простых инструкциях · В 1 кристалле процессора можно разместить большее число регистров · Меньшая зависимость от доступа к основной памяти · Повышенное быстродейтсвие Недостатки: Высокая стоимость,Затраты по переносу ПО, Более медленное выполнение сложных инструкций. Архитектура MISC: Архитектура минимального набора команд Она использует концепцию архитектуры RICS, т.е. простые короткие инструкции и упорядоченные команды используют принцип суперскалярности, плюс концепция Very Long Instruction Word (VLIM) Достоинства · Простые функциональные узлы · Отсутвует регистровая модель · Все операнды находятся в памяти и доступны всем процессорам Недостатки · Требуется интенсивная работа с памятью · Повышение требования к объему памяти · Стоимость · Сложный компилятор Суперкомпьютеры-используют концепцию «параллельн обраб данных»,основыв-я на двух направл-ях: 1) Конвейерная обработка; 2) Параллельные вычисления. Пример параллельной n-устр-ми в ед времени:

Конвейерная обработка:идея заключ-я в разбиении процесса выполнения инструкции на микроинструкции. Кажд микрооперация выполнив свою микропрогр передает результат след-ей микроинструкции одновр принима новые входные дан. Вбольш систем исп-ют 2 конвеера: конвеер команд и конвеер данных.

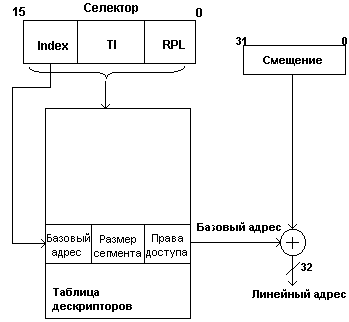

18 Архитектура 32-х разрядных процессоров. Основные характеристики. 1.Длина непрерывного сегмента памяти не ограничивается границей 64 Кб. 2. Поддерживается виртуальная память до 64 Гб. 3. 4-х уровневая система защиты пространств памяти, ввода/вывода. 4. Расширенная система команд. 5. Используются три режима адресации: -Режим реальной адресации -Защищенный режим виртуальной адресации -Режим виртуального процессора 8086 (особое состояние задачи защищенного режима) 6. Режим системного управления 7. Процессор может оперировать 8-ми, 16-ти, 32-х битными операндами, строками байт, слов, двоичных слов, а также с битами, битовыми полями и строками бит. 8. В процессоре введены средства отладки и тестирования. Регистровая модель 32-х разрядной архитектуры-явл полн совместим с предыдущ моделями мп.32-х разрядные CPU имеют регистры: 1)РОН-основные регистры мп(явл-я 16ти разрдн,хранят инф и результаты операций над инф); 2)Регистры указателей и индексов(sp-указ-ль стека,BP-указ базы,SI и DI-для работы со строков операц-ми); 3)Регистр флагов(хранит признаки результатов выполнения арифм и логич операций); 4)Регистр инструкций; 5)Регистр сегментов(содерж: сегмент кода,данных,стека,доп сегмент данных; 6)Системные адресные регистры; 7)Управляющие регистры(хрант признаки состония мп общие для всех задач); 8)Регистры отладки 9)регистры тестирования и модельно специфические регистры. 19 Защищенный режим. Характеристики. Защита памяти. Страничная преадресация Защищенный режим (Protected Virtual Address Mode) является основным режимом работы 32-х разрядных процессоров. Он предназначен для обеспечения независимого выполнения нескольких задач, что подразумевает защиту ресурсов одной задачи от воздействия другой. Основным защищаемым ресурсом является память, а также совместно используемая аппаратура, обращение к которой происходит через операции ввода/вывода и прерывания. Большинство функций защиты процессор реализует на программном уровне. Характеристики защищенного режима: 1. Защита памяти основана на сегментации. Максимальный размер сегмента 4 Гб. В защищенном режиме сегменты распределяются ОС. Прикладная программа может использовать только разрешенные для нее сегменты памяти, выбирая их с помощью селекторов из дескрипторных таблиц. Процессор может обращаться только к тем сегментам памяти, для которых имеются дескрипторы в таблицах. Механизм сегментации формирует линейный адрес по следующей схеме:

Поле TI принимает значение либо «0», либо «1». Если TI = 0 GDT (выбирается глобальная таблица дескрипторов) Если TI = 1 LDT (выбирается локальная таблица дескрипторов).

2. Защита памяти с помощью сегментации не позволяет: § Использовать сегменты не по назначению § Нарушать права доступа § Адресоваться к элементам выходящим за лимит сегмента § Изменять содержимое таблицы дескрипторов, не имея достаточных привилегий. 3. Защищенный режим предоставляет средства переключения задач. Состояние каждой задачи сохраняется в сегменте состояния задачи. При переключении задач, состояние текущей задачи автоматически сохраняется в ее TSS (сегмент состояния задачи). 4.Четырехуровневая иерархическая система привилегий. Предназначена для управления использованием привилегированных инструкций и доступа к дескрипторам. Передача управления между задачами контролируется вентилями (шлюзы), проверяющими правила использования уровня привилегий. PL (уровень привилегий) = 0 – это максимальный уровень привилегий, относится к ядру ОС. PL =1 – отводится под системные сервисы PL = 2 – расширение ОС PL = 3 приложения, минимальный уровень привилегий. Уровни привилегий относятся к дескрипторам, селекторам, задачам, а также инструкции ввода/вывода. Нарушение защиты вызывает исключения. 5. Страничное управление памятью является средством организации виртуальной памяти с подкачкой страниц по запросу. Сегментация организует программы и данные в модуле различного размера, а страничная организация оперирует с памятью как с набором страниц одинакового размера. В момент обращения страница может присутствовать в физической оперативной памяти или быть выгруженной на внешнюю память. При обращении к выгруженной странице процессор вырабатывает исключение – отказ страницы. А программный обработчик исключения получает необходимую информацию для свопинга. В оперативной памяти в каждый момент времени следует хранить только небольшие области сегментов, необходимые активным задачам. Эту возможность обеспечивает страничное управление памятью. Базовый механизм страничного управления использует двухуровневую табличную трансляцию линейного адреса в физический.

Поиск по сайту: |

Селектор – это логическое имя модулей кодов или данных.

Селектор – это логическое имя модулей кодов или данных.